Oltre il limite di scaling dei CMOS

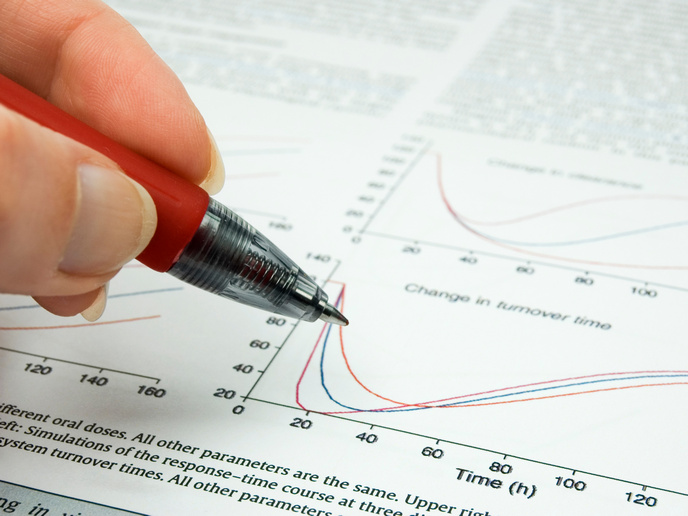

I dispositivi di memoria a singolo elettrone (SEM) offrono una soluzione interessante ai problemi tecnologici che sorgono mentre ci si avvicina al limite di scaling del CMOS (semiconduttore ad ossido di metallo complementare). Sono formati da un nano-floating gate su uno stretto canale MOSFET (transistor semiconduttore ad ossido di metallo a effetto di campo) e si basano ancora sul concetto convenzionale di "trasferimento di carica". Perciò non si garantisce solamente la compatibilità con la tecnologia CMOS convenzionale, ma riutilizzando l'enorme quantità di know-how accumulato si potrebbero risolvere gli attuali problemi di dissipazione di potenza. La tecnologia proposta dal progetto SASEM utilizza un impianto di arsenico (As) per creare un profilo gaussiano delle impurità nello strato attivo di un wafer di silicio su isolante (SOI). Dopo aver definito la mesa di silicio tramite litografia e attacco a secco, è stata effettuata un'ossidazione a umido per separarla in due cavi con l'ossido di silicio al centro. Il tasso di ossidazione è aumentato con la presenza dell'arsenico, mentre la variabilità della larghezza della mesa di silicio ha consentito la creazione di un punto quantico sopra al canale triangolare continuo. Il punto quantico è stato caricato/scaricato applicando una tensione rispettivamente di segno negativo/positivo al gate e la variazione indotta della corrente di uscita è stata usata per la lettura. Per garantire un controllo efficace della formazione e delle dimensioni del nano-floating gate, l'intero processo di fabbricazione del dispositivo è stato studiato a fondo e simulato con i modelli più affidabili. I parametri di processo fondamentali come la temperatura e il tempo di ossidazione sono stati poi ottimizzati e la riproducibilità garantita. Sono state testate le operazioni di memoria del dispositivo a singolo elettrone prodotto a temperatura ambiente e le caratteristiche di prestazione stimate sono paragonabili a quelle dei dispositivi esistenti. Mentre sono necessari dei miglioramenti prima dell'implementazione industriale della tecnologia, è stata dimostrata la fattibilità del down-scaling del dispositivo e si è più vicini all'uso degli effetti quantici nei dispositivi pratici.