Page 1 of 55

The research leading to these results has received funding from the European Union Seventh Framework Program (*FP7/2007-2013*) under grant agreement no. 284389

# **1 EXECUTIVE SUMMARY**

Several important future space-based instruments, for example synthetic aperture radar (SAR) and hyper-spectral imagers will be capable of producing data at data rates of several Gbits/s. New downlink telemetry techniques (laser and Ka-band communications) will be able to provide much higher downlink capacity than previously possible. High-speed memory technologies will be able to serve multiple high data-rate instruments and stream data to ground on demand. To support the growing need for onboard communications network bandwidth high-speed serial interfaces are necessary. The Very High Speed Serial Interface (VHiSSI) project has researched and designed an experimental high-speed serial interface chip to support spaceflight applications. This chip implements the emerging ESA SpaceFibre standard serial communications protocol and includes important quality of service (QoS) and fault detection, isolation and recovery (FDIR) capabilities. It was implemented in a new radiation tolerant chip technology and manufactured by a European foundry and tested extensively. The VHiSSI research programme has researched, designed and developed an experimental high speed serial interface chip, VHiSSI, which:

- Provides multi-Gbit/s serial data-link technology, essential for future spacecraft onboard datahandling systems.

- Levers prior and concurrent research on the emerging SpaceFibre standard, to provide a complete multi-Gbit/s serial technology for spacecraft onboard data-links and networks, including fault detection, isolation and recovery (FDIR) and quality of service (QoS).

- Provides a versatile chip architecture, which can be adapted and configured to support multiple applications.

- Provides the critical clock-data recovery mechanism on existing European chip technology.

- Uses a European semiconductor fabrication facility, enhancing and developing its capabilities for radiation tolerant chip design and production with a radiation tolerant library. Further work needs to be done related to the radiation single event effects (SEE).

- Provides a non-dependent technology allowing unrestricted use on European spacecraft and substantial export opportunities an important capability for Europe.

The principal benefits of the VHiSSI research programme are:

- Very high-speed serial-interface technology applicable to many space missions, including large and small satellites, robotic missions, planetary landers and rovers, launchers and related electronic test equipment, and which is capable of spin-out to a wide range of terrestrial applications, including demanding robotics applications.

- A high-speed serial interface chip implemented using a radiation-hard standard cell library optimized for a new 130 nm CMOS process, although further work needs to be carried out related to radiation single event effects (SEE).

- Mixed-signal high-speed radiation-hardened integrated circuits that are free from international export restrictions (non-dependent) that are fabricated and tested in Europe, and that are available to members of the European Union for use in space missions. The SEE issue detected in the last month of the project needs to be addressed and space grade qualification is necessary.

The medium term impact of the VHiSSI programme will be an independent European technology for spacecraft high-speed data-links and network technology. The VHiSSI research will lead to a complete spacecraft onboard data-handling solution, saving mass and power, improving reliability, and substantially simplifying complex system design.

#### Page 2 of 55

# **Table of Contents**

| 1 | EX                                                                            | (ECUTIVE SUMMARY2                                      |  |  |  |  |  |  |

|---|-------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|

| 2 | Pro                                                                           | Project Context and Objectives4                        |  |  |  |  |  |  |

|   | 2.1                                                                           | Context4                                               |  |  |  |  |  |  |

|   | 2.2                                                                           | Project Objectives5                                    |  |  |  |  |  |  |

|   | 2.3                                                                           | Project Team6                                          |  |  |  |  |  |  |

| 3 | Ма                                                                            | in Scientific and Technological Results8               |  |  |  |  |  |  |

|   | 3.1                                                                           | Project Overview                                       |  |  |  |  |  |  |

|   | 3.2                                                                           | WP1 Spacecraft High Speed Serial Interface Use Cases10 |  |  |  |  |  |  |

|   | 3.3                                                                           | WP2 Concepts and Specification Development14           |  |  |  |  |  |  |

|   | 3.4                                                                           | WP3 VHiSSI VHDL Core Design16                          |  |  |  |  |  |  |

|   | 3.5                                                                           | WP4 VHiSSI ASIC Research and Design19                  |  |  |  |  |  |  |

|   | 3.6                                                                           | WP5 VHiSSI PHY Layer Research and Design25             |  |  |  |  |  |  |

|   | 3.7                                                                           | WP6 VHiSSI ASIC Experimental Implementation26          |  |  |  |  |  |  |

|   | 3.8                                                                           | WP 7 ASIC Experimentation and Testing29                |  |  |  |  |  |  |

|   | 3.9                                                                           | VHiSSI Objectives Addressed49                          |  |  |  |  |  |  |

| 4 | 4 Potential Impact, Main Dissemination Activities and Exploitation of Results |                                                        |  |  |  |  |  |  |

|   | 4.1                                                                           | Potential impact                                       |  |  |  |  |  |  |

|   | 4.2                                                                           | Main dissemination activities52                        |  |  |  |  |  |  |

|   | 4.3                                                                           | Exploitation of Results                                |  |  |  |  |  |  |

| 5 | Pro                                                                           | oject Details                                          |  |  |  |  |  |  |

# 2 Project Context and Objectives

## 2.1 Context

Space-based Earth observation and scientific instrumentation currently under development will push the limits of on-board data-handling technology. In the past Mil-Std 1553 and proprietary data-links were used to get instrument data from the instruments to the on-board mass memory unit and to the down-link telemetry system. Over the past decade the proprietary data links have been replaced with a standard networking technology designed for use on-board spacecraft: SpaceWire. While SpaceWire is currently being used to fulfil the on-board data-handling requirements of many missions, there are some very high data-rate instruments which are beyond its capabilities.

Several important future space-based instruments, for example synthetic aperture radar (SAR) and hyper-spectral imagers will be capable of producing data at data rates of several Gbits/s. New downlink telemetry techniques (laser and Ka-band communications) will be able to provide much higher downlink capacity than previously possible. High-speed memory technologies will be able to serve multiple high data-rate instruments and stream data to ground on demand. To support the growing need for onboard communications network bandwidth, technologies able to support multi-Gbits/s data transfer have been developed, e.g. Channel Link and, Wizard Link. Unfortunately these are all restricted USA devices resulting in a critical European dependency.

SpaceFibre is a spacecraft onboard data-link and network technology being developed by University of Dundee for the European Space Agency (ESA) which runs over both copper and fibre optic cables. Initially targeted at very high data rate instruments like Synthetic Aperture Radar (SAR) and multi-spectral imaging instruments, SpaceFibre is capable of fulfilling a wider set of spacecraft onboard communications applications because of its inbuilt QoS and FDIR capabilities and its backwards compatibility with the ubiquitous SpaceWire technology.

SpaceFibre operates at 2.5 Gbits/s providing 12 times the throughput of a SpaceWire link with current flight qualified technology and allowing data from multiple SpaceWire devices to be concentrated over a single SpaceFibre link. This substantially reduces cable harness mass and simplifies redundancy strategies. The innovative QoS mechanism in SpaceFibre provides concurrent bandwidth reservation, priority and scheduled QoS. This simplifies spacecraft system engineering through integrated quality of service (QoS), which reduces system engineering costs and streamlines integration and test. Novel integrated FDIR support provides galvanic isolation, transparent recovery from transient errors, error containment in virtual channels and frames and "Babbling Idiot" protection. SpaceFibre enhances onboard network robustness through its inherent FDIR and graceful degradation techniques incorporated in the network hardware. This simplifies system FDIR software, reducing development and system validation time and cost. SpaceFibre includes low latency event signalling and time distribution with broadcast messages enabling a single network to be used for very high data rate payload data, carrying SpaceWire traffic, deterministic information for command/control, time distribution and event signalling.

#### Page 4 of 55

SpaceFibre is backwards compatible with existing SpaceWire equipment at the packet level allowing simple interconnection of SpaceWire devices into a SpaceFibre network and enabling that equipment to take advantage of the QoS and FDIR capabilities of SpaceFibre.

Present implementations of SpaceFibre using separate SerDes and FPGA devices are dependent on USA components.

# 2.2 Project Objectives

The primary motivation for the proposed VHiSSI project was to provide Europe with important very high-speed serial interface technologies, enhancing the technical capabilities and overall competitiveness of the European space industry, enabling it to compete effectively on the world market.

The VHiSSI research programme has the following key objectives:

- A justified set of requirements and use cases for the VHiSSI chip, which takes into account requirements from spacecraft primes and equipment manufacturers, across the EU.

- A consolidated concept and architectural design, which takes into account relevant literature and concurrent research and technology development work on the SpaceFibre standard and applications, explores and analyses alternative designs, and trades-off alternative solutions.

- A detailed specification for the VHiSSI chip, based on the requirements and use cases and the conceptual design and analysis work.

- A design for the digital part of the VHiSSI chip implemented in an FPGA and validated against the requirements and use cases.

- A radiation tolerant design of the VHiSSI chip using a European foundry.

- A design of the high-speed SerDes component including clock recovery and drivers/receivers targeted for the process available from the European foundry.

- An implementation of the experimental VHiSSI chip, packaged ready for experimentation and testing.

- Characterisation of the functionality, performance and radiation tolerance of the VHiSSI chip.

- System level validation of the VHiSSI chip against the requirements and flight representative use cases.

- Disseminated results of the VHiSSI research programme to the ESA, European space industries, and to the international space community.

- An exploitation plan covering the development of flight grade chips, and an appropriate market strategy including support to European space missions, and export opportunities.

## 2.3 Project Team

To achieve these goals, technological spin-in from the European microelectronics research community and multi-lateral collaboration between leading European institutions and industry, both large prime contractors and SMEs, was essential to provide the necessary breadth of technical knowledge, capability and experience. A highly experience team of European academic and industrial organisations was assembled for the VHiSSI project:

The University of Dundee (UNIVDUN) has long experience in spacecraft onboard network technology, writing the SpaceWire standard with support from the European Space Agency (ESA) and input from engineers across Europe. UNIVDUN has extensive experience in related IP core design having designed SpaceWire interface, remote memory access protocol (RMAP) and router cores for ESA, JAXA and other organisations.

The principal responsibilities of UNIVDUN were overall project management, initial requirements and use cases (in conjunction with Airbus DS), devising the architectural concepts and specification, designing an independent test bench for the VHiSSI chip and, in conjunction with STAR-Dundee, functional and performance characterisation and system level testing of the VHiSSI chip.

**Airbus DS GmbH** is a major international spacecraft manufacturer that undertakes system integration and also designs and manufactures spacecraft payloads.

The principal responsibilities of Airbus were the requirements and use cases for VHiSSI based on their extensive spacecraft design experience and the functional characterisation of the VHiSSI chip in Total Ionising Dose (TID) and heavy ion characterisation for Single Event Effects.

**STAR-Dundee Ltd** is a world leading supplier of SpaceWire IP cores and test and development equipment. STAR-Dundee specialises in spacecraft on-board data-handling systems and the IP cores and test and development equipment needed to successfully realise these systems.

The principal responsibilities of STAR were the design, simulation and FPGA-based validation of the VHiSSI VHDL core, the design and manufacture of the VHiSSI test boards, and, in conjunction with UNIVDUN, functional and performance

#### Page 6 of 55

characterisation and system level testing of the VHiSSI chip.

**ACE-IC Ltd** is a fabless Analog-Mixed Signal design house specializing in design applications for the Communication industry, in particular the next generation of rapid information transfer applications. ACE-IC has expertise in designing Multirate SerDes (from 1Gbps up to 12Gbps) which supports several tele/data communication protocols.

The principal responsibilities of ACE-IC were the design of a radiation tolerant, high-speed SerDes for the VHiSSI chip.

**RAMON CHIPS Ltd.** is a fabless semiconductor company focused on developing unique VLSI /ASIC solutions for space applications. RAMON has expertise in designing digital and analogue radiation-hardened chips from specifications, synthesis of functions and algorithms into robust radiation-tolerant cores, and converting FPGA designs into radiation-hardened ASICs.

The principal responsibilities of RAMON were the definition of the test and validation plan for the experimental ASIC, and design of the experimental ASIC and the RadHard libraries.

**IHP** carries out research and development in the area of microelectronics and information technology. IHP's core competences are in materials research, semiconductor technology, RF-circuit design and system development in a closed innovation chain. The IHP pilot line provides production facilities for internal projects but can also be used by third parties through MPW & prototyping services.

The principal responsibilities of IHP were manufacturing and supporting the testing of the VHiSSI chip, development of the advanced and nonstandard rad-hard cells and improvements to the rad-hard design flow.

**Synergie-Cad Instruments srl** (SCI) is an Italian company dedicated to providing testing services to semiconductor companies and fabless.

The principal responsibilities of SCI were load board schematics development, test program development, test program and load board debug.

innovations for high performance microelectronics

Leibniz-Institut für innovative Mikroelektronik

RAMON**Chips**

# 3 Main Scientific and Technological Results

## 3.1 Project Overview

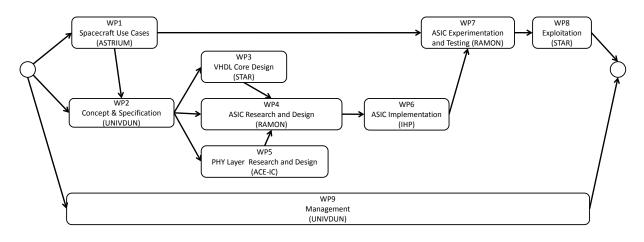

An overview of the project is illustrated in Figure 3-1. There are seven technical work packages, one specifically looking at exploitation, and a management work package.

#### Figure 3-1 Overall strategy of the work plan

The research began with WP1 (Spacecraft Use Cases) where a comprehensive set of requirements for the experimental VHiSSI chip were gathered from the European spacecraft engineering community by Airbus DS GmbH, focusing on a small device which could be used to provide very high-speed data-links on-board a spacecraft. A set of uses cases for VHSSI were also devised taking into account information from spacecraft prime and equipment manufacturers across Europe. From the use cases a corresponding set of test scenarios were derived for use in the system level validation of the VHSSI.

WP2 (Concepts and Specification) provided the overall architectural concept for VHSSI. Research on the system architecture examined the potential use of VHSSI in high-speed networking onboard future spacecraft. The functional, performance and interface specifications for the VHSSI chip were derived from the requirements produced in WP1. A versatile chip interface was designed by University of Dundee which covers many potential applications while keeping the number of pins required on the chip to a minimum.

WP3 (VHDL Core Design) focused on the digital design for the VHSSI chip which was carried out by STAR-Dundee Ltd. The VHDL RTL code for the VHSSI chip was designed based on the specifications developed in WP2. Following successful simulation and testing, an FPGA implementation of VHiSSI was produced and used to perform extensive system-level experimentation and validation based on the test scenarios devised in WP1 in preparation for the backend ASIC design tasks in WP4.

WP4 (ASIC Research and Design) covered the research and development of radiation-tolerant, highspeed circuits suitable for manufacturing on the IHP European foundry. The use of the IHP chip foundry required a complete radiation tolerant component library to be designed. The design was based on RadSafeTM libraries, developed by Ramon Chips, and ported to the IHP 0.13u process. It utilizes several Radiation Hardening By Design (RHBD) techniques, which provides high immunity to all radiation effects. The libraries included standard cells, IO cells including LVDS buffers, and SRAMs with complementary EDAC logic for enhanced soft error protection. The library test components from Ramon Chips were implemented in the RADIC 5 test chip and validated. Some small improvements were made to the library for the VHiSSI device. The VHiSSI chip logic design from STAR-Dundee Ltd (WP3) and the improved SerDes from ACE-IC (WP5) was designed into the IHP chip technology by Ramon Chips including floor planning, place and route, and timing extraction. STAR-Dundee Ltd supported this activity carrying out static timing analysis of the placed and routed design. The chip was then manufactured by IHP on its 130 nm Bi-CMOS process (WP6).

In WP5 (PHY Layer Research and Design) the serialiser/deserialiser, clock-data recovery circuitry and the high-speed serial driver/receiver technology (SerDes) was carried out by ACE-IC. This was a particularly demanding design activity due to the speed of the interface and the required radiation tolerance. The SerDes core, which was designed by ACE-IC, was based on guidelines provided by Ramon Chips for hardening against radiation effects. The design of the SerDes was tested in the RADIC5 test chip and various improvements subsequently made for the VHiSSI chip. The output of WP5 fed into the chip design of WP4.

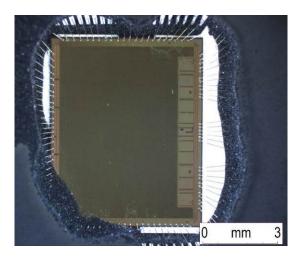

In WP6 (ASIC Implementation) first the RADIC5 test chip and then the experimental VHiSSI chip were implemented on the 130 nm European chip technology from IHP. The resulting VHiSSI chip is shown in Figure 3-2.

#### Figure 3-2 VHiSSI SpaceFibre Chip

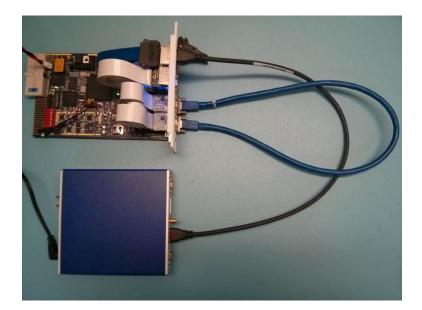

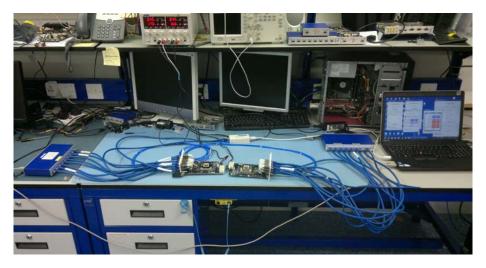

In WP7 (ASIC Experimentation and Testing) the VHiSSI chip was extensively evaluated. While the chip was being manufactured in WP6, SCI, IHP and STAR-Dundee Ltd developed test vectors for chip testing and STAR-Dundee Ltd designed, implemented and tested four test boards for the VHiSSI chip covering different functions. VHiSSI chip was encapsulated into a plastic package and initial chip testing carried out on a chip tester at IHP. The chips that passed these tests were then used by

Page 9 of 55

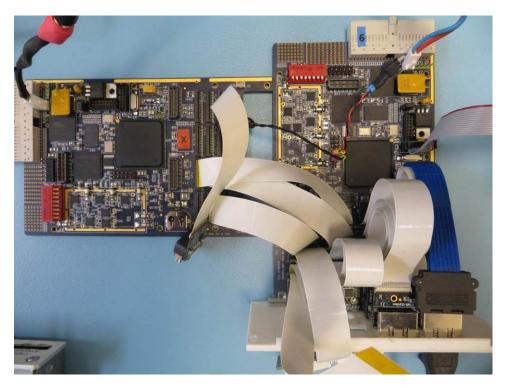

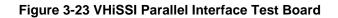

STAR-Dundee Ltd, University of Dundee and ACE-IC for the functional and performance testing (see Figure 3-3). Experiments were conducted to assess many aspects of the device including: functionality, performance and system level validation.

Figure 3-3 Testing the VHiSSI SpaceFibre and SpaceWire Interfaces

Throughout the programme of work presentations were made to the international SpaceWire Working Group and to relevant conferences to ensure engagement with the broader spacecraft onboard networking and data link community. WP8 (Exploitation and Dissemination) focused on this dissemination and the formulation of an exploitation plan.

WP9 ran in parallel with all the other work packages to provide efficient and effective management of the project. Overall project management was carried out by an experienced management team at UNIVDUN.

The results of each work package will now be described in more detail.

# 3.2 WP1 Spacecraft High Speed Serial Interface Use Cases

An initial set of requirements and use cases were developed for the VHiSSI chip taking into account the needs of European aerospace industry. The initial requirements and use cases were presented to the 18th International SpaceWire Working Group meeting in April 2012, by Paul Rastetter of Astrium. This formed the starting point of a more general presentation on SpaceFibre technology, which also included an overview of the VHiSSI aims and outline chip concept. Informal feedback from various SpaceWire working group members was very positive. At the SpaceWire Interagency Meeting on 25th April, support was provided for the SpaceFibre concept from all parties, including ESA, NASA, JAXA and RosCosmos, with several groups interested in conducting parallel prototyping activities.

The primary applications envisaged for the VHiSSI chip are listed below:

• SpaceWire to SpaceFibre Bridge i.e. harness mass and power reduction and longer distance communication.

- Instrument to Mass Memory or Processor

- Mass memory from Instruments

- Mass Memory to Downlink Telemetry

- Downlink Telemetry from Mass Memory.

- Control Processor controlling instruments and other units

- Data Processor Array

- Integrated Avionics Network

- Long distance control connection for launcher using Fibre Optics.

- VHiSSI Chip Applications

Several important use cases for the VHiSSI chip are considered in the following subsections.

#### 3.2.1 High Data-Rate Instrument Interface

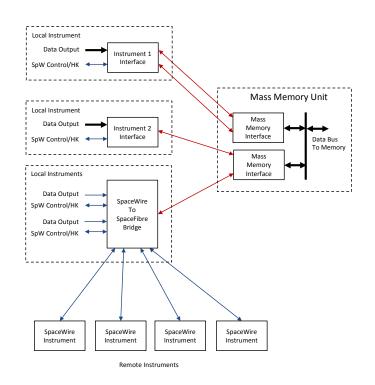

SpaceFibre offers substantially higher data rates than SpaceWire to support high data-rate instruments. Connection of a high data-rate instrument to a mass memory unit via SpaceFibre is illustrated in Figure 3-4.

Figure 3-4 High Data-Rate Instrument Connected To Mass Memory

To provide data at high-speed from a local instrument to the SpaceFibre interface a parallel interface is required. To operate with current space qualified FPGAs this interface has to be 32 bits wide, which requires a 62.5 MHz interface clock (32-bits x 62.5 MHz = 2 Gbits/s, which after 8B/10B encoding is 2.5 Gbits/s signalling rate).

The simplest type of interface is a FIFO type interface, which is straightforward to connect to an FPGA. For high data rate transfer from an instrument it is only necessary to write data to an output VC buffer in the SpaceFibre interface. A slower speed interface, e.g. SpaceWire, would be useful for controlling and reading housekeeping information from the instrument.

If the instrument includes an embedded processor it may be preferable to use a memory type interface to write and read data from the SpaceFibre VC buffers in the SpaceFibre interface. This interface can then also be used to access the configuration, control and status registers inside the SpaceFibre interface. In this case it is the responsibility of the instrument to handle the transfer of data to the SpaceFibre interface.

A DMA controller included in the SpaceFibre interface transfers responsibility for data transfer from the instrument controller to the SpaceFibre interface. This may save some important processing power within the instrument controller.

The VHiSSI device is able to provide a SpaceFibre interface for high data rate instruments using a FIFO, memory or DMA type interface to an FPGA or processor. This interface is designed to be able to operate at clock speeds achievable by flight qualified FPGAs while sustaining 2 Gbits/s data transfers. It also is designed to minimise the number of pins required for the interface.

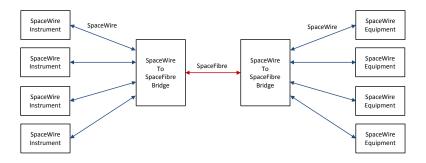

## 3.2.2 SpaceWire to SpaceFibre Bridge

SpaceWire has been used extensively to provide a standard interface to various instruments. To connect these instruments into a SpaceFibre based data-handling network a SpaceWire to SpaceFibre Bridge is required.

Figure 3-5 SpaceWire to SpaceFibre Bridge

Figure 3-5 shows a SpaceWire to SpaceFibre Bridge being used to multiplex several SpaceWire links over a single SpaceFibre link. In this particular example four instruments with SpaceWire interfaces are connected to some other SpaceWire enabled equipment. Bridging between SpaceWire and SpaceFibre is straightforward since both protocols use the same packet format.

The VHiSSI chip can operate as a SpaceWire to SpaceFibre bridge with either LVDS or LVTTL SpaceWire interfaces and includes an internal SpaceWire router.

### 3.2.3 Mass Memory Interface

A mass memory requires several SpaceFibre interface connections to support several high data-rate instruments and instruments with SpaceWire interfaces. This is illustrated in Figure 3-6.

Figure 3-6 Mass Memory Interface

Two high data-rate instruments are shown, one with a single SpaceFibre link and the other requiring two SpaceFibre links to support data rates of 4 Gbits/s. Several SpaceWire instruments are also connected to the mass memory via a SpaceWire to SpaceFibre Bridge.

The Mass Memory unit provides four SpaceFibre interfaces connected to a common bus or network for accessing the memory modules that are to store the data.

The VHiSSI chip can provide all the SpaceFibre interfaces required in the example network of Figure 3-5: high-speed instrument interfaces, SpaceWire to SpaceFibre bridge and the interface to the mass memory unit.

## 3.2.4 Control Processor

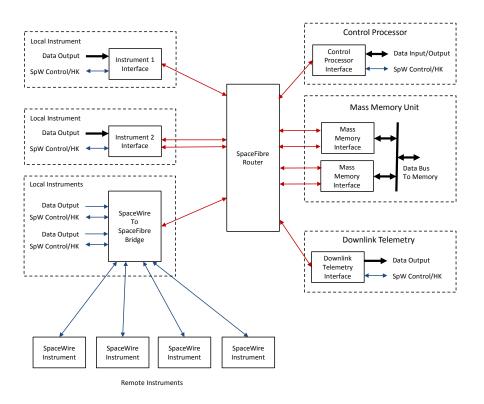

Configuration and control information can be sent over a SpaceFibre network using individual virtual channels or a virtual network. A SpaceFibre router allows a control processor to access all the instruments and other equipment on the network as illustrated in Figure 3-7.

Figure 3-7 Control Processor on SpaceFibre Network

Figure 3-7 shows a complete SpaceFibre based on-board data-handling system. A SpaceFibre router is used to interconnect the various units. A control processor is connected to this router. It is able to send configuration, control and status request commands to all of the other units on the network. Typically a virtual network would be used to manage this control and status information, where one virtual channel in each unit is dedicated to control/status and each of them is given the same virtual channel number, e.g. VC0. The control processor then sends SpaceWire packets containing commands over VC0 to another unit. This unit responds over VC0. Since the control processor is the master of the VC0 virtual network, there is no undesirable contention between SpaceWire packets on VC0. This approach leaves all the other virtual channels available for data transfer.

The SpaceWire instruments do not support virtual channels, so control/status packets and data packets have to be multiplexed over the SpaceWire links. The SpaceWire to SpaceFibre Bridge must be able to support this multiplexing of SpaceWire packets containing control information, status or instrument data. This requires a SpaceWire router which could be provided within the SpaceWire to SpaceFibre Bridge. Normally configuration, control and housekeeping requests require small packets and should therefore not have a major impact on data transfer over the single SpaceWire link from instrument to the SpaceWire router in the SpaceWire to SpaceFibre Bridge.

The VHiSSI device together with a SpaceFibre router device can provide all the SpaceFibre network functionality needed for onboard data-handling architectures like that of Figure 3-7.

## 3.3 WP2 Concepts and Specification Development

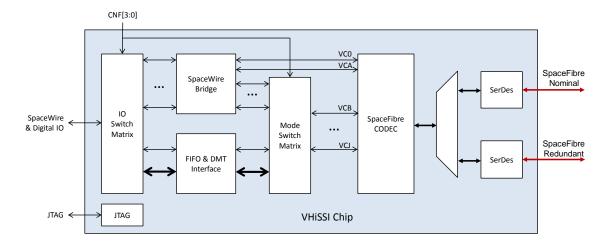

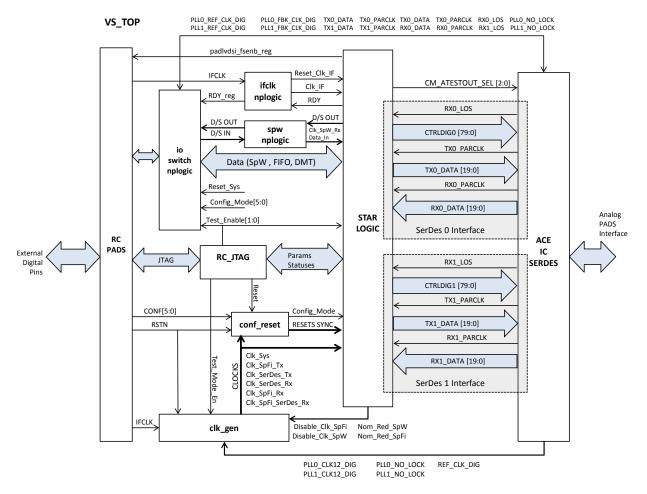

The overall architectural block diagram of the VHiSSI chip is illustrated in Figure 3-8. Page 14 of 55

#### Figure 3-8 VHiSSI Overall Architecture

There are five main functions within the VHiSSI chip:

- SpaceWire Bridge

- FIFO, DMA, Memory and Transaction Interface

- SpaceFibre Interface

- SerDes

- IO Switch Matrix

- Mode Switch Matrix

The SpaceWire Bridge provides a bridge between SpaceWire and SpaceFibre with up to 11 SpaceWire interfaces being available. The SpaceWire Bridge includes a SpaceWire router which allows routing between SpaceWire ports and Virtual Channel (VC) buffers of the two SpaceFibre interfaces. Configuration of the VHiSSI chip can be carried out over any SpaceWire interface connected to the embedded SpaceWire router or over VC0 or VC1 of the SpaceFibre interface. The SpaceWire Bridge is connected to the IO Switch Matrix and to the Mode Switch Matrix.

The FIFO and DMA, Memory and Transaction (DMT) Interface provides various types of parallel interface into the VHiSSI chip for sending and receiving data over the SpaceFibre interfaces. The various parallel interface functions have been designed with specific application scenarios in mind and between them are able to operate with many types of local host system, including FPGAs and processors. The parallel interface is also designed to use a small number of pins, so that the VHiSSI chip can fit into a small (100 pin) package. The FIFO mode provides a direct parallel interface to two SpaceFibre virtual channels. The memory type interface provides a 32-bit bus interface for accessing VHiSSI registers or VC buffers. It is a multiplexed address/data bus, with the VHiSSI device providing an internal address latch/counter to hold the register/VC buffer address. The transaction interface is used to distinguish commands and status information from data. A command is written to the VHiSSI device to specify the transaction that is about to take place. For data transfer to/from a VC buffer, a

Page 15 of 55

read of status information provides the status of the VC buffer identified in the command. The data transfer can then take place in a burst transfer the maximum size of which is determined by the VC buffer status information. The DMA interface puts the VHiSSI chip in control of data transfers. When there is data ready to transfer, an internal DMA controller in the VHiSSI device requests control of the external data bus. Once granted it then affects the data transfer. An external address latch/counter is required, which may be implemented in an FPGA. The FIFO and DMT interface is connected to the IO Switch Matrix and to the Mode Switch Matrix. On reset the IO pins and connections to the VC buffers from the FIFO and DMT interface and SpaceWire Bridge are determined and set by these two switch matrices.

The SpaceFibre Interface has 11 virtual channels. VC 0 is intended primarily for VHiSSI device and local system configuration and monitoring and is connected to the embedded SpaceWire router. VC1 is connected to the embedded SpaceWire router. The other VCs are either connected to the SpaceWire router, directly to a SpaceWire interface, or to the parallel interface, depending on the mode of operation. Each VC supports full SpaceFibre QoS which can be configured independently for each VC. VC0 and VC1 are directly connected to the embedded SpaceWire router. The other SpaceFibre VC buffers are connected to the Mode Switch Matrix which connects them to either the SpaceWire Bridge or the parallel interface. The other side of the SpaceFibre interface is connected via a multiplexer to either the nominal or redundant SerDes and CML transceiver.

The SerDes converts parallel data words from the SpaceFibre interface into a serial bit stream and vice versa. On the receive side the bit clock is recovered from the serial bit stream by the SerDes. The SerDes includes integral CML transceivers.

The IO Switch Matrix connects either the SpaceWire LVDS, SpaceWire LVTTL or parallel interface signals from the FIFO and DMT interface to the digital IO pins of the VHiSSI chip. Configuration is static and determined on exit from device reset, i.e. on the rising edge of the RSTN signal.

The Mode Switch Matrix connects either the SpaceWire Bridge or FIFO and DMT interface (parallel interface) to the VC buffers of the two SpaceFibre interfaces. Configuration is static and determined on exit from device reset, i.e. on the rising edge of the RSTN signal.

In addition to these major functions the VHiSSI chip includes a JTAG test port and some other device test modes.

The architecture of the VHiSSI chip was translated into a detailed specification for the VHDL code, which was then implemented in WP3.

# 3.4 WP3 VHiSSI VHDL Core Design

## 3.4.1 VHDL Coding

In WP3 the VHDL code for the VHiSSI chip was implemented by STAR-Dundee. A test bench for the VHiSSI VHDL code was designed by UNIVDUN. STAR and UNIVDUN then carried out simulation and

Page 16 of 55

testing of the VHiSSI VHDL code using the test bench. The VHDL code was then implemented in an FPGA and tested using a specially designed test board.

## 3.4.2 VHiSSI FPGA Test Board

A test board was designed, manufactured and tested containing an FPGA into which the VHiSSI design could be programmed (see Figure 3-9). The VHiSSI VHDL code was placed and routed for the FPGA on the test board and post layout simulation carried out to check that the place and routing had not introduced any errors. The VHiSSI design was then loaded into the FPGA test board and initial testing was then carried out. Functional validation against the requirements from WP1 was then performed and system level validation done for the SpaceWire to SpaceFibre bridge mode and parallel interface mode. The resulting VHiSSI VHDL code was extensively tested ready for ASIC implementation.

Figure 3-9 VHiSSI FPGA Test Board

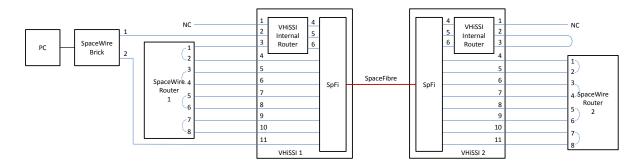

## 3.4.3 SpaceWire-SpaceFibre Bridge Mode Validation

The validation of VHiSSI as a SpaceWire-SpaceFibre bridge was carried out using a SpaceFibre interface unit (STAR Fire) to generate SpaceFibre packets (see Figure 3-10). This setup tested the bridging from SpaceFibre to SpaceWire and from SpaceWire to SpaceFibre. The VHiSSI FPGA implementation passed all the tests for this mode of operation.

Figure 3-10 Photograph of SpaceWire to SpaceFibre Bridge Test Setup

### 3.4.4 Parallel Interface Mode Validation

To test the VHiSSI FPGA in the FIFO mode of operation two VHiSSI FPGA test boards were used (see Figure 3-11); one programmed as a VHiSSI chip and the other as a tester board. A script file (which was also used during VHDLS simulation testing) was used to define the tests to be executed by the tester. Two test scripts were created: one containing a core set of tests to exercise the main functionality of the VHiSSI FPGA in FIFO mode, and one containing a full set of tests, consisting of the core set plus additional steps, e.g. to test the switching between the nominal and redundant SerDes. Some of the functionality of the Xilinx SerDes used in the VHiSSI FPGA implementation, such as implementation of a redundant channel, does not correspond to the functionality of the SerDes model used in simulation. Therefore, while the full set of tests was used during simulation, the FPGA testing carried out up to this point used the core set. This set of tests exercises the key functionality of VHiSSI in FIFO mode, and the VHiSSI FPGA implementation passed all the tests in this set.

Figure 3-11 Photograph of Parallel Interface Test Setup

The same test architecture used for FIFO mode validation was used for DMT mode validation, with a script file defining the test steps to be executed. This has been tested in simulation, but time did not permit these tests to be carried out on the VHiSSI FPGA implementation.

# 3.5 WP4 VHiSSI ASIC Research and Design

RAMON carried out the design of the radiation tolerant circuits for the VHiSSI device. RAMON adopted the RadSafe design methodology, which was proved on other products and other process flows, and ported it to IHP 0.13u process. The porting included porting of the schematics and layout to the new process, performing layout verifications, a complete timing characterization and generating the required technology files that enabled the automatic logic and physical synthesis of the RTL based logic design. The key concepts of this methodology are:

- Radiation Hardening is achieved by design No need for special CMOS process

- Based on standard CMOS technology

- Same technology for all space applications

- Radiation hardening guaranteed by similarity to previously qualified products/test chips

- All IPs fully developed and owned by RAMON. They are completely ITAR free.

The effects mitigated by RadSafe methodology are:

- TID

- SEL

- SEU/SET in flip-flops

- SEU in SRAMs

#### Page 19 of 55

The mitigation techniques used are:

- TID special layout constrains, special SRAM cell

- SEL special layout constrains

- SEU/SET special flip-flop circuits, special methodology for clock tree & resetting

- SEU in SRAM implementing EDAC

#### 3.5.1 Logic Gates

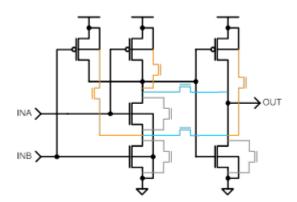

The mitigation of TID effects is done by fix geometry of the transistors, and the parasitic structures. An example of the parasitic devices that are controlled by this methodology is presented in Figure 3-12 which shows an AND gate, with its parasitic devices, controlled in RadSafe technology.

Figure 3-12: Parasitic devices

The mitigation of SEL is done by adequate physical design of the cell libraries. The topology of the PNPN structure, which might latch, is identical in all cells, thus once some of the cells are proven to be immune to SEL, it is true for the rest of the library. The mitigation is achieved by increasing the "holding voltage" of the PNPN devices to be above VDD, thus long term latching is disabled completely.

The mitigation to SEU is achieved by using proprietary circuit, which cannot be upset by flipping of a single node. This is the concept of the flip-flops. The SET effect is mitigated by implementing glitch filter at the input of every flip-flop.

#### 3.5.2 SRAMs

The SRAM cells, which need to be very compact, are also implementing proprietary mitigation technique, which was proven in previous products. It uses 6T circuits, but unlike the conventional circuits, it use 4 PMOS transistors and 2 NMOS transistors. The path transistors, connecting to the bit lines, are implemented by PMOS transistors, which do not leak after TID stress, thus no degradation mechanism exists in this structure. The SEU rate per bit, as measured in previous test chips, was about 10X better than in commercial libraries that is not enough in most space applications, thus EDAC or an alternative fault tolerance technique is needed.

Page 20 of 55

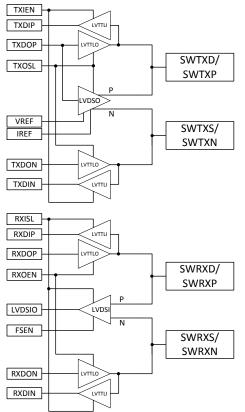

## 3.5.3 IO Cells

A combined structure for the IO cells was proposed and implemented in RADIC5. The concept is illustrated in the Figure 3-13. This configurable I/O enables several additional modes of operation, which enhances the performance and flexibility of the VHiSSI significantly. It enables the following features:

- Either 10 single ended SpaceWire ports or 5 differential (LVDS) SpaceWire ports

- TTL2LVDS mode, for additional applications and for easy testing

- LVDS2TTL mode, for additional applications and for easy testing

Figure 3-13: Schematics of the configurable TTL/LVDS IO buffers

## 3.5.4 RADIC5 testing, studying and measuring circuits

This section describes the activities for testing, studying and measuring the circuits including the SerDes on the selected 130nm process using the RADIC5 test chip.

## 3.5.4.1 Goals of RADIC5 chip

The goals of the RADIC5 test chip were:

- Characterization of the analogue core in bypass mode (eye opening, jitter, BER, etc.)

- Characterization of all I/O cells (VIL/VIH, VOL/VOH, I/O leakage, Vid/Vic of LVDS, etc.)

- I/V characteristics of standard core transistors and their sensitivity to TID stress

Page 21 of 55

The research leading to these results has received funding from the European Union Seventh Framework Program (*FP7/2007-2013*) under grant agreement no. 284389

- Speed of ring oscillators, accuracy of the device models and the speed degradation due to TID stress

- Verification of large shift register block, designed with automatic synthesis flow

- Verification of JTAG and boundary scan logic

#### 3.5.4.2 RADIC5 Blocks

The Blocks used in the RADIC5 are listed below:

- SerDes core analogue core of dual channel SerDes, as provided by ACE-IC

- IO block the complete ring of I/O pads, with all bonding pads and ESD circuits

- XTOR block individual RadSafe NMOS and PMOS transistors for I/V characterizations

- RINGS block 3 ring oscillators/delay lines.

- Logic block a synthesized logic core, which includes the following functions:

- Switch matrix, to enable operation of the chip in all modes

- JTAG block, which enables boundary scan, and loading the configuration register

- SHFTR block, large block, with 5 shift registers, each one with different flip-flop

- PRBS generator and checker, for characterizing the analogue SerDes

#### 3.5.4.3 RADIC5 Fabrication

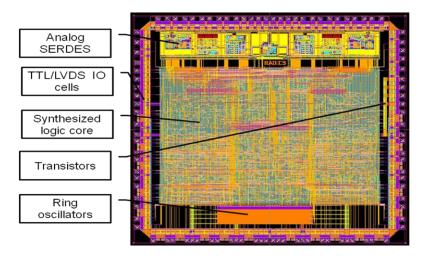

The fabrication of the RADIC5 test chip was completed by IHP and packaging was handled by RAMON. The chip layout can be seen in Figure 3-14.

#### 3.5.4.4 RADIC5 Testing

The testing of the digital core was completed by IHP and RAMON. The testing of the SerDes by EIT/SCI and ACE-IC was not achieved and STAR took ownership on this task, created a test board and performed, together with ACE-IC, all testing that led to the findings, which were applied to the final delivery of the SerDes.

The test plan was defined by ACE-IC for the SerDes core and by RAMON for the rest of the chip. The testing of the SerDes core was achieved by testing the SerDes on the board level testing. The test vectors have been generated, but not used.

The testing of the digital parts was done by IHP, based on the test plan and test patterns generated by RAMON. This stage was completed successfully, indicating that all the tested functions are performing correctly.

The list of tests performed is listed in Table 1.

Table 1: RADIC5 testing

| # | Test                                | Test<br>H/W    | Owner                        | Comments                                                                                          | Status                           |

|---|-------------------------------------|----------------|------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------|

| 1 | Functional &<br>parametric test     | VLSI<br>tester | ihp,<br>Ramon                | RAMON provided test patterns & test plan.<br>IHP developed the test program                       | Completed                        |

| 2 | SerDes<br>characterization<br>board | VLSI<br>tester | EIT/SCI,<br>ACE-IC,<br>RAMON | ACE-IC defined test plan. EIT/SCI developing the test H/W & program. RAMON provided test patterns | Completed<br>using STAR<br>board |

| 3 | Characterization of transistors     | SPA            | IHP                          | Should be done before and after TID stress                                                        | Complete                         |

| 4 | TID testing                         | STAR           | ASTRIU<br>M STAR             | Logistics & testing should be coordinated with IHP & EIT/SCI                                      | Will be done<br>to VHiSSI        |

### 3.5.4.5 Lessons learnt for VHiSSI chip

The following lessons were learnt for the VHiSSI chip during the testing of the RADIC5 test chip:

- All vias should be duplicated.

- Should consider the use of the multi-IO buffers with ODT to enable termination of input signals.

- Filler cells should not have any sensitivity to yield. Capacitance is less important.

- Assembly of the VHiSSI devices should come from several wafers, and defect density of the yield monitors should be considered when selecting the wafers to be assembled.

- The EVCD files should include all the pins, including the analogue pins and IREF/VREF pins (even if it defined as high impedance).

- Test Rule Checker (TRC) should be run as "tapeout procedure" to the test patterns.

- In LVDS+TTL buffers, verify that pull-up transistor is disconnected when LVDS is active.

- Timing of all inputs should be aligned, as much as possible, to simplify the patterns. In many cases, the NRZ signals can change at FE of CLK.

## 3.5.5 Integration and verification of the VHiSSI experimental device

In this section the Integration and verification of the VHiSSI experimental device, done by RAMON are described. The VHiSSI top level architecture is shown in Figure 3-15.

Figure 3-15: VHiSSI Top Level

Top level contains the following main modules:

- **RC\_PADS**: IO pads provided by RAMON including LVTTL and LVDS drivers.

- **RC\_JTAG**: JTAG controller designed by RAMON.

- **STAR\_LOGIC**: Designed by STAR. Provides the main functionality of VHiSSI including the SpaceWire router and the SpaceFibre codec. It also includes the BIST controller designed by RAMON.

- ACE\_IC\_SerDes: Designed by ACE-IC. Provides an analogue core that implements a SerDes.

In addition, there are some small modules in the Top Level module:

- **io\_switch\_nplogic**: Connects the various digital interfaces within the VHiSSI chip to the digital IO pins, depending on the strapping pins and the *Test\_Enable* signal. Also contains some registers that shall be located close to the pads.

- **conf\_reset**: Creates the synchronous resets for *Clk\_Sys* and *Clk\_IF* domains and latches the values of the CNF[5:0] pins when RSTN pin is low.

Page 24 of 55

- **ifclk\_nplogic**: Contains the logic related with the *Clk\_IF* domain that needs to be placed as close as possible to the pads (Near Pad Logic). Generates the *Clk\_IF* signal. Registers the *RDY* signal close to the output pad.

- clk\_gen: Generates all clocks except the Clk\_IF.

- **spw\_nplogic**: Defines the logic related with the *Clk\_Spw\_Tx* domain that needs to be placed as close as possible to the pads (Near Pad Logic). Recovers the *Clk\_Spw\_Rx* clocks immediately after Data and Strobe signal enter the chip to minimise the skew between them, and also recovers the SpW input bit stream with this clock.

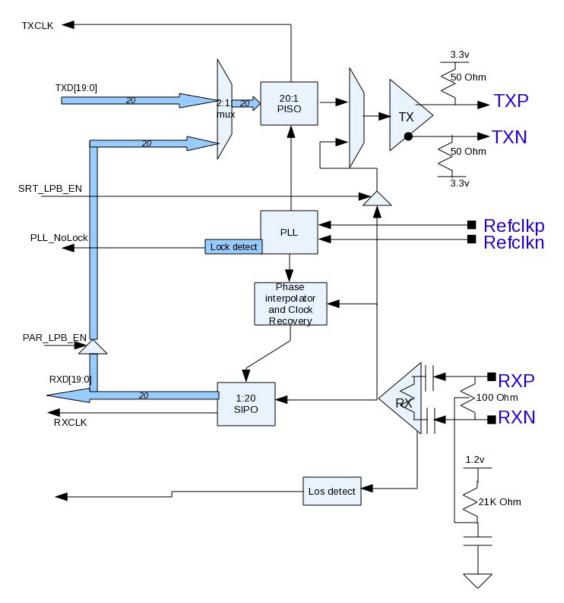

## 3.6 WP5 VHiSSI PHY Layer Research and Design

The SerDes is a key element of the VHiSSI chip which converts parallel data to high-speed serial data and vice versa. A block diagram of the final SerDes is illustrated in Figure 3-16.

Figure 3-16 - SerDes Block Diagram

Page 25 of 55

The transmit data (TXD[15:0] is passed via a 2:1 multiplexer into the parallel in to serial out (PISO) converter which converts the 20-bit encoded data into a serial bit stream. The serial bit stream is then passed to the transmit driver providing the differential CML transmit signals (TXP and TXN). A transmit clock operating at 1/20 of the required data rate is proved by a PLL in the SerDes to be used for loading of parallel transmit data into the SerDes.

The serial received CML data (RXP and RXN) is received by the CML receiver and passed via a 2:1 multiplexer to a serial in parallel out (SIPO) converter, to the clock recovery circuit and to a loss of signal detector (LOS). The SIPO converter takes the serial data and a recovered clock signal provided by the clock recovery circuit, samples the received signal, takes 20-bits of the serial data and converts them to 20-bit parallel data. A receive clock at 1/20 of the received data rate is provided for transferring the decoded parallel data out to user logic.

The PLL is provided with a reference clock from which it generates the transmit clock, and a reference clock for the Phase Interpolator and Clock Recovery circuit. The Phase Interpolator and Clock Recovery circuit locks to the phase of the received signal to provide a receive sampling clock.

The loss of signal detector (LOS) detects when there is no signal present at the input of the receiver.

Two loopbacks are provided: a serial loopback that connects the receive serial data signal to the input of the transmitter and a parallel loopback that connects the received parallel data output to the transmit parallel data input. These loopback circuits are controlled by signals STR\_LPB\_EN and PAR\_LPB\_EN respectively.

The PHY circuits were layout by ACE-IC, RAMON provided the STD cells and I/O cells and customized the ESD to meet low capacitance requirement of the SerDes.

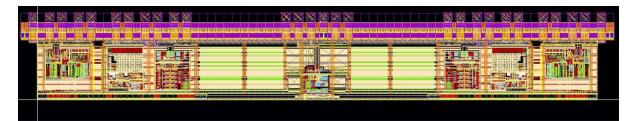

The final SerDes layout is shown in Figure 3-17.

## 3.7 WP6 VHiSSI ASIC Experimental Implementation

WP6 focused on implementation, packaging and initial tests of the final VHiSSI chip. The VHiSSI chip design was exported to the IHP fab on April 2014 and it was included in a multi project wafer (MPW) run. Chips were produced in the period April - July 2014 and selected wafers passed the acceptance tests defined by IHP- internal rules. Diced chips were sent to the subcontractor MAF for packaging. After receiving the 90 packaged devices, the initial test campaign started in the second half of August.

## 3.7.1 Chip Fabrication Process

The VHiSSI chip was submitted to the MPW run for 130 nm technology. This technology was still at the research stage and was not commercially qualified. Some basic information about the clean room of IHP is provided in the following Figure 3-18. Also the view to the IHP clean room during fabrication process is given in Figure 3-19.

| CLEANROOM SIZE           | ~ 1000 m² Class 1       |

|--------------------------|-------------------------|

| TECHNOLOGY               | RF SiGe:C BiCMOS        |

| WAFER SIZE               | 200 mm                  |

| CAPACITY                 | 100 Wafer Starts / Week |

| TOOL SET CAPABILITY      | 0.25μm / 0.13 μm        |

| MODE OF OPERATION        | 24h, 7 Days / Week      |

| SiGe:C BiCMOS Cycle Time | ≥1.7 Days / Mask level  |

#### Figure 3-18 Summary of IHP Clean Room Features

Figure 3-19 View to the IHP Clean Room

The VHiSSI chip was submitted to the multi-project wafer (MPW) run. That means that several chips share the mask costs and that they are fabricated in parallel.

### 3.7.2 VHiSSI Packaging

The package selected for VHiSSI is a 14x20mm 100L QFP. It provides sufficient IOs, and the electrical performance of the traces is marginally acceptable for the required data rate of the SerDes.

The bonding diagram of VHiSSI is the presented in Figure 3-20. The lead frame was replaced relative to the one used in RADIC5 to the selected one in order to have a larger die pad, required for larger die size, and shorter lead traces, which have less inductance. The increase of the die size and shortening the bond wires provides an additional advantage, thus the total reduction of the inductance

Page 27 of 55

of the lease is 1-2nHy, or 10-20%. This improvement in package performance will be translated to some improvement in signal integrity of the high speed signals.

#### Figure 3-20 Bonding diagram of VHiSSI chip (die pad is 9.5x9.5mm)

The device is packaged in plastic QFP package for the purpose of this project. It is possible to convert this package to an equivalent hermetic ceramic package, with similar dimensions and similar electrical performance, which will allow this product to be modified to space qualified package. This is an option for future productisation of this product and qualifying it for space.

## 3.7.3 VHiSSI Initial Test

After receiving the packaged chips, the initial test campaign was started in IHP with staff support from STAR and Synergie-CAD. 90 packaged devices were received and it was decided to perform the tests on 65 devices while 25 were kept as a backup. The following sets of tests were made using a VLSI tester.

- Continuity test

- Static IDD

- Reset test

- IDDQ Test

- IO Tests lvds2lvttl and lvttl2lvds

- Functional FIFO tests (only limited tests available)

- Functional SPW tests (only limited tests available)

- Functional memory BIST tests (due to an error in the design only one memory block had BIST connected).

- SerDes DC Tests

- SerDes Power down

- SerDes Power up

#### Page 28 of 55

- SerDes Power down/ Rx on

- o SerDes Vout-Bref

- SerDes Vout-Power up

From the tested 65 chips, the pre-selection process had already discarded 11 chips based on the continuity tests (determined by packaging). The other main tests such as static ldd, lddq, functional, SerDes tests discarded an additional 2-5 chips, with the tendency that the same chips usually failed on multiple tests.

Although the current tests have shown very promising results and low dispersion of the measured current values among the different chips, the open question regarding the yield has been opened with the BIST test which revealed 11 erroneous chips, with only testing the single block of memory. The next system level test will determine whether the memory yield could be an issue for system testing of the SerDes or not.

As a final result, of the initial testing 36 chips (out of 54 passing continuity) have been selected as suitable for use in the next phase of system testing, SerDes characterization and radiation testing. Test vectors to test most of the chip functionality were not ready in time for the tests on the VLSI tester so these tests were carried out in WP7 using dedicated test boards.

# 3.8 WP 7 ASIC Experimentation and Testing

The VHiSSI chips that passed the testing on the VLSI tested at IHP were subject to further testing and experimentation by STAR-Dundee, UNIVDUN and ACE-IC. To support this testing several test boards were designed by STAR-Dundee.

## 3.8.1 Test Boards

This section describes the circuit boards necessary for the experimentation on the SpaceFibre-HSSI chip. Four test boards were required to test the different VHiSSI operational modes and to support radiation testing:

- VHiSSI SpaceWire LVDS Test Board

- VHiSSI SpaceWire LVTTL Test Board

- VHiSSI Parallel Interface Test Board

- VHiSSI Radiation Test Board

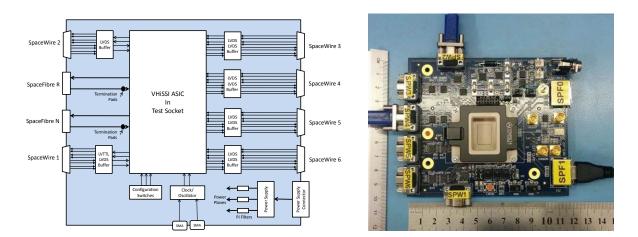

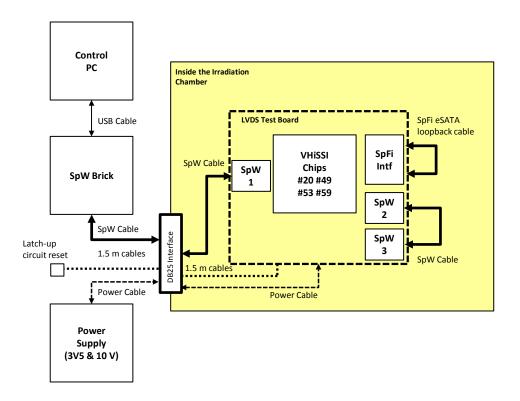

The VHiSSI SpaceWire LVDS Test Board is used to test the SpaceWire to SpaceFibre bridge mode of the VHiSSI chip using the inbuilt LVDS drivers for SpaceWire giving 5 LVDS SpaceWire ports and one LVTTL port. This board was also designed to support the single event effect (SEE) radiation testing. A block diagram and photograph of the SpaceWire LVDS board is shown in Figure 3-21.

Figure 3-21 VHiSSI SpaceWire LVDS Test Board

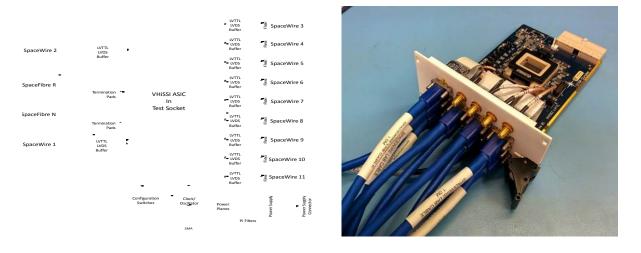

The VHiSSI SpaceWire LVTTL Test Board is used to test the SpaceWire to SpaceFibre bridge mode of the VHiSSI chip using the inbuilt LVTTL drivers for SpaceWire giving 11 SpaceWire LVTTL ports. A block diagram and photograph of the SpaceWire LVTTL board is shown in Figure 3-22.

Figure 3-22 VHiSSI SpaceWire LVTTL Test Board

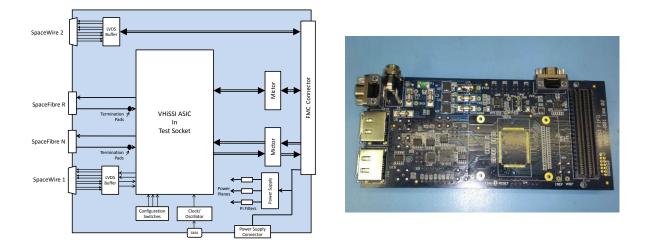

The VHiSSI Parallel Interface Test Board is used to test the VHiSSI chip operating with the parallel interface to the VHiSSI chip including the FIFO, Memory and DMA interfaces. A block diagram and photograph of the Parallel Interface board is shown in Figure 3-23.

## 3.8.2 SerDes Testing

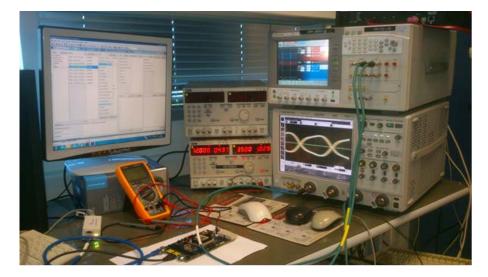

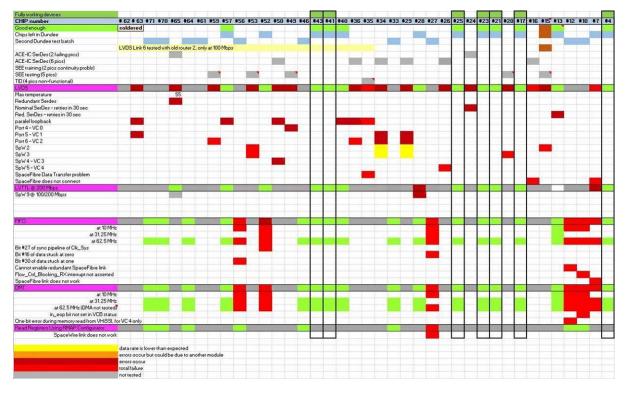

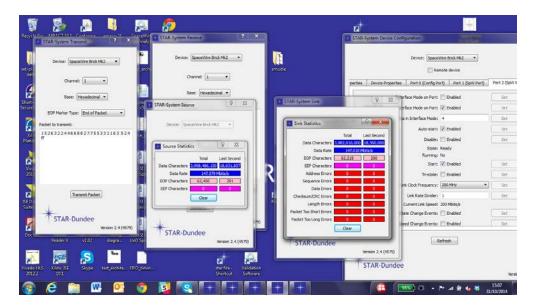

The SerDes characterisation test setup is shown in Figure 3-24.

Figure 3-24 SerDes Characterisation Test Setup

A SpaceWire-USB Brick is connected to one of the VHiSSI SpaceWire LVTTL board's SpaceWire connectors and to the host PC through its USB interface. Software provided by STAR-Dundee is used to control the system and change registers values in the VHiSSI chip. A JBERT Bit Error Rate Tester is connected to the receive (RX) side's high speed serial SpaceFibre interface and is used as serial data source generator to create clock patterns and PRBS patterns. The oscilloscope or JBERT input is connected to the transmit (TX) side to measure serial output signal transmitted from the chip. When a RX to TX parallel loopback is closed, the data received by the VHiSSI chip should be transmitted back out of the VHiSSI chip.

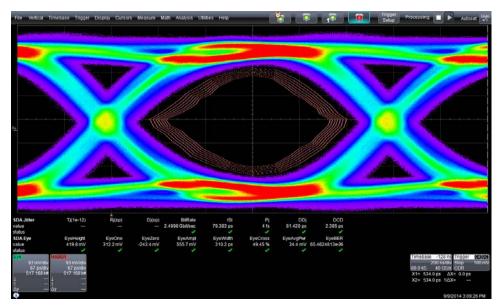

The overall performance of the SerDes was within the expected design values. The design improvements made to the SerDes in the VHiSSI chip following the results of the RADIC 5 testing

were all found to operate as intended, significantly improving the SerDes operation. The eye pattern of the SerDes is shown in Figure 3-25.

| eysight Infiniiu   | a : Thursday, Octo | ber 30, 2014 1                                                                                                  | 0:17:54 PM       |            |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GHT               |

|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------|------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| un Stop Single 🥂   | 20.0 GSa/s 5.00    | Mpts $\sim\sim$                                                                                                 |                  | ~~~{}~~    |                             | ~~~ 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10 GHZ) 🕤 🧐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .00 mV            |

| aveform Window 1   |                    |                                                                                                                 |                  | 6.45 A     |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                 |

| T 🗄 😥 500 3        | 00 mV/ 0.0 V       | 350 150 mV/                                                                                                     | -293 mV          | <b>8</b> = |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

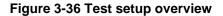

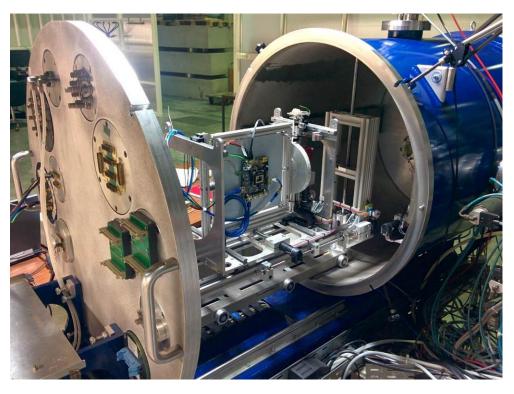

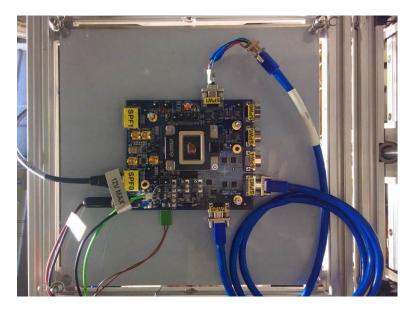

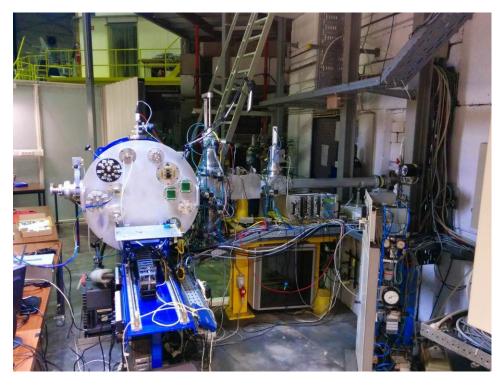

| Time Meas          |                    |                                                                                                                 |                  | ŧ          |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.20<br>900 n     |