## **NANOFUNCTION**

## **Beyond CMOS Nanodevices for Adding Functionalities to CMOS**

### **Network of Excellence**

## Nanosensing with Si based nanowires

Deliverable D1.1: Pros and cons of nanowire fabrication techniques for sensor arrays

Main Author(s): T. Baron, P.-E. Hellström, L. Latu-Romain, M. Mongillo, L. Montès, M. Mouis, L. Poupinet, J.-P. Raskin, B. Salem and M. Schmidt.

Due date of deliverable: 31 August 2011 Actual submission date: 1 September 2011

# LIST OF CONTRIBUTORS

| Part. Nr. | Acronym      | Organisation name                                                                     | Name of contact |

|-----------|--------------|---------------------------------------------------------------------------------------|-----------------|

| 2         | INP Grenoble | Institute Polytechnique de Grenoble                                                   | M. Mouis        |

| 5         | KTH          | Kungliga Tekniska Hoegskolan                                                          | PE. Hellström   |

| 8         | UCL          | Université catholique de Louvain                                                      | JP. Raskin      |

| 14        | AMO-GMBH     | Gesellschaft fuer angewandte mikro-<br>und optoelektronik mit beschrankter<br>haftung | M. Schmidt      |

| 15        | CEA          | Commissariat à l'Energie Atomique                                                     | L. Poupinet     |

## **TABLE OF CONTENTS**

D1.1

| Deliverable summary       | 5 |

|---------------------------|---|

| 1. Introduction           | 6 |

| 2. Fabrication techniques |   |

| 2.1 Bottom-up fabrication |   |

| 2.2 Top-down fabrication  |   |

| 3. Conclusions            |   |

| References                |   |

## **Deliverable summary**

Pros and cons of fabrication techniques for silicon nanowires (SiNW) is reviewed with respect to a multifunctional sensor application based on silicon nanowires integrated with CMOS. Bottom-up approaches is generally simple and can provide high quality SiNW with nanometer dimensions. We have drastically improved the morphology and composition control in the growth of SiGe NWs using bottom-up approach. However complex integration with CMOS and lack of ability to position many SiNW in an ordered way is still a challenge for bottom-up approaches. This last point could be solved by using an assembly of nanowires. Top-down approaches has less severe integration issues with CMOS technology. Electron beam lithography (EBL) has been used to pattern SiNW for sensors but throughput is still an issue for an application with many nanowires. In recent year advanced optical lithography and sidewall transfer lithography (STL) has evolved and has been shown to produce SiNW in the 10-50 nm range with high reproducibility and throughput. Within Nanofunction SiNW fabrication processes that are compatible with CMOS technology using EBL, advanced optical lithography and STL has been developed.

#### 1. Introduction

Silicon nanowires (SiNW) have been shown to be an excellent sensing element to detect charged molecules due to the large surface to volume ratio. The sensitivity of an individual SiNW has shown to outperform planar structures such as nanoribbons for the same response time [1]. Furthermore it was found that reducing the dimension of the sensing element to Si dots does not substantially improve the sensitivity. Sensing applications includes detection of molecules in gases and in liquids and for several applications it is desirable to sense several different molecules with one sensor. This can be achieved by placing SiNW in a matrix and integrate them with CMOS for reading the state of an individual SiNW. To achieve the substantial potential of SiNWs in the area of a multifunctional sensor it will be required to achieve controlled and predictable assembly of well-ordered SiNWs. In this deliverable we report on the different SiNW fabrication processes and their applicability for a SiNW matrix sensor integrated with CMOS.

## 2. Fabrication techniques

The fabrication process of SiNWs can be divided into "bottom-up" and "top-down" approaches. We review the fabrication technologies for SiNW and describe pros and cons for a SiNW matrix sensor. We report the state-of-the-art and work performed during the first year within Nanofunction.

## 2.1 Bottom-up fabrication

Bottom-up nano-fabrication is in principle simple and provides many high quality materials. Silicon whiskers grown from the well-known vapour-liquid-solid (VLS) reaction have been extensively investigated [2-8]. In the VLS reaction, metal particles, for example gold particles on Si substrate, are generally used as the mediating solvent to direct the growth of SiNWs. Up to date, many other methods such as oxygen-assisted-growth (OAG) [9], [10], vapor-solid-solid (VSS) [11], electroless etching methods and laser-assisted catalytic growth (LAC) [12-14], have been developed to synthesize large-scale SiNWs.

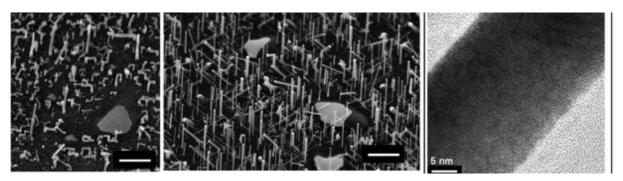

In Nanofunction we have developed a generic process (same temperature and total pressure) to grow Si, Ge and SiGe NWs with Au as a catalyst based on the addition of HCl in the gas phase [15]. We found that diameter uniformity, growth stability and morphological quality are also drastically improved. The SiGe NWs were grown in a hot-wall reduced pressure chemical vapour deposition system via the VLS process on Si (111) substrates. Si and Ge are provided by pure silane (SiH4) and germane (GeH4 5% in H2). We have studied the growth of SiGe NWs as a function of 1) gas phase composition, 2) gas ratio:  $R = \Phi_{GeH4}/(\Phi_{SiH4} + \Phi_{GeH4})$  where  $\Phi_X$  is the flow of the precursor x expressed in sccm, and 3) growth temperature. Growth temperature and gas ratio have been fixed at 400°C and R=0.15 respectively. Fig. 1 shows SiGe NWs obtained with HCl flows varying between 0 and 90 sccm. Without HCl most of the NWs are highly kinked and the few straight NWs are slightly tapered. Moreover, an uncatalyzed growth of nanocrystals on the substrate can be observed. When 40 sccm of HCl is introduced along with process gases, the NWs are straights, and no tapering or uncatalyzed deposition on the substrate can be observed by SEM. TEM image show that the NW are single crystalline and grow along the (111) direction.

Fig. 1 SEM pictures of SiGe NW grown at 400 °C with R=0.15. Left image is without HCl and middle is with 40 sccm HCl. Right shows a HRTEM image of a single SiGe NW.

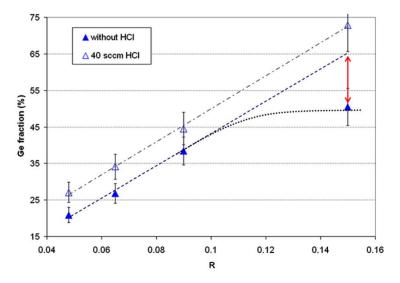

The gas flow ratio R was changed by keeping the germane flow constant (4.5 sccm of pure GeH4) and by varying the SiH<sub>4</sub> flow between 90 and 25 sccm (R varies between 0.048 and 0.15). Fig. 2 shows that the Ge fraction without using HCl evolves linearly between 20.9 and 38.4 % as R is changed from R=0.048 to R=0.09 (dark triangles). Then the Ge fraction tends to reach a saturation value around 50%. When we added 40 sccm HCl (white triangles), no saturation of the Ge fraction was observed.

Fig. 2 Ge fraction of the SiGe NWs grown at 400 °C as a function of the GeH₄ gas flow ratio R. Without HCl, the Ge fraction for R=0.15 does not follow (red arrow) the linear tendency high-lighted for low R (dashed line). At 40 sccm flow of HCl, the Ge fraction seems to follow a linear increase (dashed-dot line) as a function of R

The HCl effect on Ge fraction was found to be temperature dependent. At 400°C and 425°C, an increase of the Ge fraction from 50% to 70% is observed when using 40 sccm HCl. At 450°C, two HCl flow rates have been used. At 40 sccm HCl induces an increase from 50% to 65% of the Ge content and at 90 sccm HCl leads to an increase of the Ge content from 50 to 85%. These results clearly show a remarkable effect of HCl addition in the gas phase on the Ge fraction in the NWs, which depends both on the growth temperature and on the flow rate of HCl. HCl improves the NWs' morphology and density of straight NW at reduced flow rates ( $\Phi_{\text{HCl}} \ge 40$  sccm) and deteriorates or inhibits the growth at higher flow rates ( $\Phi_{\text{HCl}} \ge 60$  scmm). HCl also

improves the incorporation of Ge atoms in the SiGe NWs and allows the growth of Ge rich SiGe NWs under conditions where Ge fraction would saturate at lower values without HCl. The SiGe NWs growth rate is decreased as HCl is introduced in the gas phase. Finally, HCl effects turn out to be temperature dependent and allow extending the process window toward higher growth temperatures. By adjusting HCl flow and temperature we are able to control precisely the morphology and the composition of the NWs for a broad range of growth temperature.

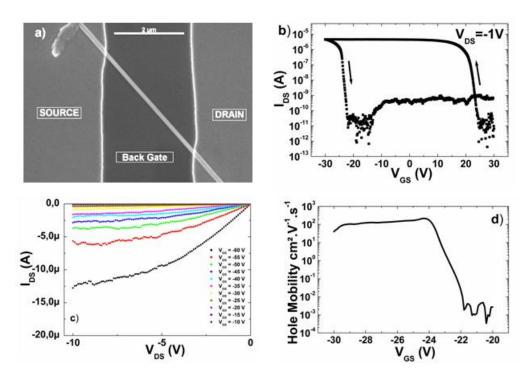

A potential drawback using gold and copper as catalyst to direct the growth of SiNWs by VLS or VSS techniques is the possibility of inducing defect levels in SiNWs, which would trap electrons and holes in Si, and then depress the optical and electronic properties of the nanowires. The bottom-up approach which is based on self-assembled chemical vapor deposition growth techniques has some limitations, such as complex integration, requiring transfer to substrates, difficulties in positioning an individual nano- structure, making reliable ohmic contacts and making it demanding to construct functional device arrays [16-28]. Nevertheless within Nanofunction high performance silicon nanowire filed-effect transistors with silicided contacts has been demonstrated (see Fig. 3) [29].

Fig. 3 SiNWs FETs with 200 nm Si3N4 back gate insulator: (a) A SEM view of the device showing S/D electrodes and a single SiNW bridging both contacts. (b)  $I_{DS}$ - $V_{GS}$  characteristic of a SiNW FET recorded at  $V_{DS}$  =- 1 V. The on-off current ratio of this device is  $2\cdot10^5$ . (c) typical  $I_{DS}$ - $V_{DS}$  characteristic of the devices. A saturation region is observed for high drain voltages inferior to -5 V. Measures were performed with a negative to positive gate voltage sweep which explains that the OFF-state occurs for negative gate voltages. d) Hole mobility reported as a function of the gate voltage at VDS = -1 V showing a maximum of 200 cm²/Vs estimated from the transconductance of the device. The  $I_{DS}$ - $V_{GS}$  in (b) was smoothed before the transconductance dlDS/dVGS was calculated.

The control of doping concentrations in self-assembled semiconducting nanostructures remains a challenge, and the fabrication of high-density sensor arrays is also very difficult. So far gold has dominated as the catalyst for growing Si nanowires via the vapour–liquid–solid (VLS) mechanism. Unfortunately, gold traps electrons and holes in Si and poses a serious contamination problem for Si complementary metal oxide semiconductor (CMOS) processing. To overcome this limitation, potential solutions exist and CMOS compatible catalysts based on silicides for Si NWs growth could be envisioned for SiGe NWs growth [30].

In an effort to address the problem of accurately position a huge amount of SiNW grown by "bottom-up" techniques hybrid approaches has been developed [31-35]. The grown-in-place approach is a kind of hybrid approach, in which electron beam lithography (EBL) as well as optical lithography are used to define catalyst metal in prospect channel and VLS growth is used to fabricate SiNWs guided by the catalyst.

Wafer- or chip-scale bonding and epitaxial growth represent the two most widely used methods for achieving these types of integrated systems. Nanowires were grown by chemical vapor deposition. The next step involves transferring these processed elements, with the use of an elastomeric stamp—based printing technique, from the source substrates to a device substrate.

The overall process involves (i) optimized growth of designed NWs by nano-cluster directed growth and (ii) patterned transfer of NWs directly from a NW growth substrate to a second device substrate via contact printing Devices and circuits are then fabricated on the printed arrays of NWs using conventional top-down lithography and metallization processes [32].

The hybrid approach extends the manipulation for nanostructures, and it becomes one of the major techniques for making SiNWs-related nano devices presently. These new assembly-based approaches overcome processing limitations of conventional planar CMOS technology and thus could make them formidable methods for the future high-performance 3D integrated circuits.

#### 2.2 Top-down fabrication

Top-down nanopatterning techniques provide a different path for fabricating high-density, high-quality nanoscale sensors that can be integrated with Si-based signal processing and communication circuits. Several key advantages favoring top-down Si-NW nanofabrication include well established techniques for nanopatterning, semiconductor doping, electrical contact formation, and, very importantly, the commercial availability of high quality silicon-on-insulator (SOI) substrates [36-56].

Arrays of SiNWs with 15 nm lateral dimensions have been realized with nanoimprint lithography [37]. This is a relatively low cost technology that allows high resolution patterning, but the throughput is rather low. In addition, the replication stamp fabrication is complicated and can be costly depending on the life expectancy of the stamp. Furthermore patterning on wafer scale remains problematic.

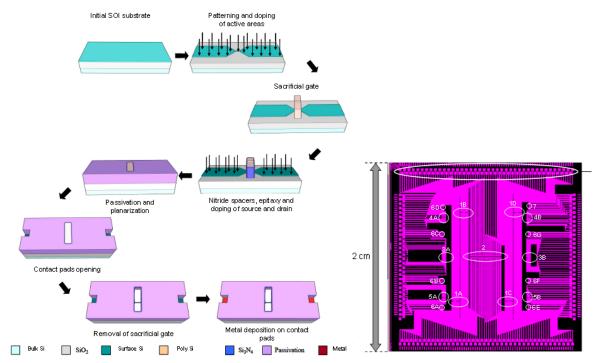

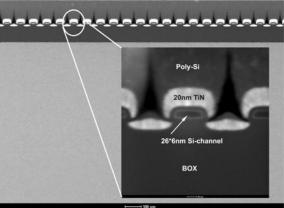

Conventional top-down nanopatterning techniques, such as deep-UV and immersion deep-UV photolithography are currently the standard for semiconductor manufacturing. However, these techniques are extremely expensive and demand a high volume application in order to be cost-effective. Generally they are only accessible to large-scale integrated circuit manufacturers. Within Nanofunction advanced optical lithography (LETI) is used to directly pattern SiNWs with

dimensions down to 35 nm in width and length. Combined with electron beam lithography SiNW with lengths and widths down to 3 nm is fabricated. The main fabrication steps are depicted in Fig. 4. The choice has been to develop CMOS compatible fabrication steps in order to be able to integrate the sensors with its addressing and readout circuits. By doing so, the way toward a possible industrialization is considerably eased. 200 mm wafer are being used with industrial processing tools. The wafers with SiNWs will be cut into chips (see Fig. 4 for layout) to be able to provide samples.

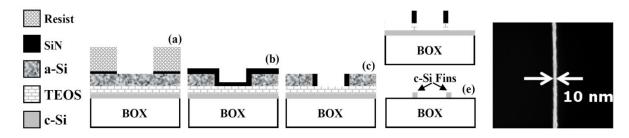

Fig. 4 CMOS compatible fabrication steps (left) to realize SiNWs with sub 10 nm dimensions as sensing element. The Layout of SiNW chip is depicted to the right (Nanofunction partner LETI).

For low volume applications G and I-line optical stepper lithography can be cost effective. However, these top-down patterning techniques can not directly pattern sub 100 nm features. Using Sidewall Transfer Lithography (STL) it is possible to pattern sub-30 nm wide SiNW with the high throughput achieved with stepper lithography [57], [58]. STL is a patterning technique in which lines are patterned by a combination of optical lithography and a spacer patterning process. A support material is patterned by optical lithography and etched anisotropic. A spacer is created on the sidewalls of the support material by conformal deposition and anisotropic etching. The support material is then removed by an etch leaving the spacer as mask for subsequential etching. Within Nanofunction (KTH) a STL process have been developed with the aim of being integrated with CMOS and provide uniform SiNW with low line width roughness. SiNWs with widths down to 10 nm and low line width roughness of 1.5 nm has been achieved (see Fig. 5) using amorphous Si as the support material and standard CMOS process technology.

Fig. 5 Schematic of the STL process using an a-Si support layer to minimize the sidewall roughness. Top view SEM picture shows a 10 nm wide SINW by STL with LWR=1.5 nm (Nanofunction partner KTH).

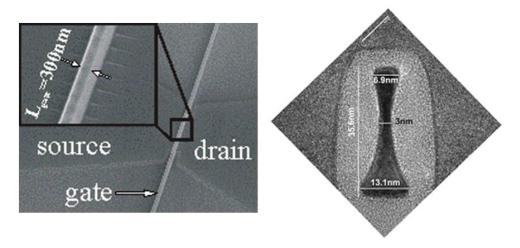

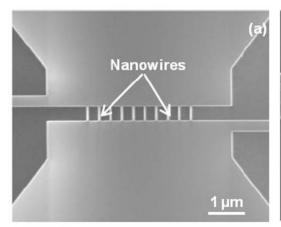

Advanced nanopatterning, such as electron beam lithography and focused-ion beam lithography can write feature sizes below 10 nm; however, serial patterning is not practical for wafer-scale fabrication and equipment and operation is typically expensive. The essential advantage of this approach is the complete control over physical and electronic degrees of freedom. The geometry and alignment of the nanowire can be fully controlled by e-beam lithography and standard semiconductor processing techniques. Furthermore, physical gate electrodes next to the nanowire can be fabricated with complete control over their location and size [40]. These local gate electrodes enable controlled accumulation or depletion of surface charge carriers on the nanowire and provide the ability to tune the nanowire conductance necessary for the optimization of the detection sensitivity. At AMO and UCL top-down process platforms for fabrication of SiNW using high resolution e-beam lithography has been developed. At AMO NW FETs are fabricated in a top-down process using silicon-on-insulator (SOI) substrates. Single and multi-wire devices (see Fig. 6) with cross sectional dimensions down to 3 nm and gate lengths from 50 nm up to 100µm show an excellent switching behavior with a sub threshold swing down to S = 74mV/dec.

Fig. 6 SEM image of a SiNW FET (left) with 300 nm gate length and 12 parallell channels. At right a cross-sectional TEM image depicts a fabricated SiNW device (Nanofunction partner AMO).

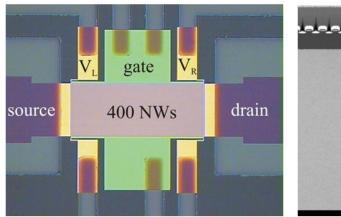

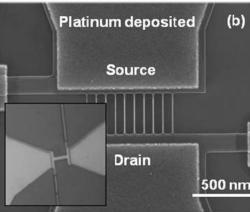

N-type SiNW MOSFETs have been fabricated in a gate first process on SOI material (100) with silicon thicknesses of 20 nm and 10 nm and a boron doping level of 10<sup>15</sup> cm<sup>-3</sup>. The SiNWs have been patterned by electron beam lithography with an HSQ mask using a novel approach combining multi-pass grey scale electron beam lithography with proximity effect correction [59]. At UCL SiNW arrays (see Fig. 8) using e-beam lithography has been fabricated for gas detection (accepted for publication in IEEE Electron Device Letters).

Fig. 7 Optical micrograph top view image (left) of a SOI SiNW nMOSFET with 400 SiNWs in parallel. To the right a TEM image shows cross section of the channel of a fully functional GdSiO/TiN nanowire n-MOSFET with sub-10 nm silicon channels (Nanofunction partner AMO).

Fig. 8 Top-view SEM image of SiNW: (a) after resist development, (b) after lift-off of platinum on the source and drain pads (Nanofunction partner UCL).

#### 3. Conclusions

Silicon nanowires can be fabricated with bottom-up and top-down approaches. The bottom-up approaches are often simple and can provide high density of NWs with high crystalline quality materials. We have shown that morphology and composition can be drastically improved using HCl in the Au catalyst growth of SiGe NWs. Although work has been progressing in recent years (e.g. FETs for sensors have been built) bottom-up approaches generally suffer from complex planar integration scheme for individual nanowires and it is difficult to predictably position many SiNW needed for a multifunctional sensor. Solutions involving large assembly of dispersed nanowires or direct integration of vertical NW arrays should therefore be preferred for low-cost sensors integration using bottom-up technologies. Top-down approaches have less severe integration issues with CMOS technology although electron beam lithography suffers from low throughput. In recent years advanced optical lithography and sidewall transfer lithography has improved and SiNW with dimensions in the 10-50 nm range can be fabricated with high throughput on wafer scale.

# References

[1] P. R. Nair and M. A. Alam, "Performance limits of nanobiosensors," *Applied Physics Letters*, vol. 88, no. 23, p. 233120, Jun. 2006.

Date of submission: 01/09/2011

D1.1

- [2] Y. L. Bunimovich, Y. S. Shin, W.-S. Yeo, M. Amori, G. Kwong, and J. R. Heath, "Quantitative real-time measurements of DNA hybridization with alkylated nonoxidized silicon nanowires in electrolyte solution.," *Journal of the American Chemical Society*, vol. 128, no. 50, pp. 16323-31, Dec. 2006.

- [3] Y. Shan, A. K. Kalkan, C.-Y. Peng, and S. J. Fonash, "From Si Source Gas Directly to Positioned, Electrically Contacted Si Nanowires: The Self-Assembling 'Grow-in-Place' Approach," *Nano Letters*, vol. 4, no. 11, pp. 2085-2089, Nov. 2004.

- [4] Y. Cui, Q. Wei, H. Park, and C. M. Lieber, "Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species.," *Science (New York, N.Y.)*, vol. 293, no. 5533, pp. 1289-92, Aug. 2001.

- [5] S.-W. Chung, J.-Y. Yu, and J. R. Heath, "Silicon nanowire devices," *Applied Physics Letters*, vol. 76, no. 15, p. 2068, 2000.

- [6] A. M. Morales, "A Laser Ablation Method for the Synthesis of Crystalline Semiconductor Nanowires," *Science*, vol. 279, no. 5348, pp. 208-211, Jan. 1998.

- [7] J. D. Prades et al., "Ultralow power consumption gas sensors based on self-heated individual nanowires," *Applied Physics Letters*, vol. 93, no. 12, p. 123110, Sep. 2008.

- [8] F. Patolsky, G. Zheng, and C. M. Lieber, "Fabrication of silicon nanowire devices for ultrasensitive, label-free, real-time detection of biological and chemical species.," *Nature protocols*, vol. 1, no. 4, pp. 1711-24, Jan. 2006.

- [9] R.-Q. Zhang, Y. Lifshitz, and S.-T. Lee, "Oxide-Assisted Growth of Semiconducting Nanowires," *Advanced Materials*, vol. 15, no. 78, pp. 635-640, Apr. 2003.

- [10] C.-P. Li, C.-S. Lee, X.-L. Ma, N. Wang, R.-Q. Zhang, and S.-T. Lee, "Growth Direction and Cross-Sectional Study of Silicon Nanowires," *Advanced Materials*, vol. 15, no. 78, pp. 607-609, Apr. 2003.

- [11] Y. Wang, V. Schmidt, S. Senz, and U. Gösele, "Epitaxial growth of silicon nanowires using an aluminium catalyst.," *Nature nanotechnology*, vol. 1, no. 3, pp. 186-9, Dec. 2006.

- [12] Y. Cui and C. M. Lieber, "Functional nanoscale electronic devices assembled using silicon nanowire building blocks.," *Science (New York, N.Y.)*, vol. 291, no. 5505, pp. 851-3, Feb. 2001.

- [13] Y. Cui, X. Duan, J. Hu, and C. M. Lieber, "Doping and Electrical Transport in Silicon Nanowires," *The Journal of Physical Chemistry B*, vol. 104, no. 22, pp. 5213-5216, Jun. 2000.

- [14] Y. Huang, X. Duan, Q. Wei, and C. M. Lieber, "Directed assembly of one-dimensional nanostructures into functional networks.," *Science (New York, N.Y.)*, vol. 291, no. 5504, pp. 630-3, Jan. 2001.

- [15] A. Potié et al., "Controlled growth of SiGe nanowires by addition of HCl in the gas phase," *Journal of Applied Physics*, vol. 110, no. 2, p. 024311, Jul. 2011.

- [16] J.-in Hahm and C. M. Lieber, "Direct Ultrasensitive Electrical Detection of DNA and DNA Sequence Variations Using Nanowire Nanosensors," *Nano Letters*, vol. 4, no. 1, pp. 51-54, Jan. 2004.

- [17] Q. Li et al., "Precise Alignment of Single Nanowires and Fabrication of Nanoelectromechanical Switch and Other Test Structures," *IEEE Transactions On Nanotechnology*, vol. 6, no. 2, pp. 256-262, Mar. 2007.

- [18] D. Whang, S. Jin, Y. Wu, and C. M. Lieber, "Large-Scale Hierarchical Organization of Nanowire Arrays for Integrated Nanosystems," *Nano Letters*, vol. 3, no. 9, pp. 1255-1259, Sep. 2003.

- [19] P. A. Smith et al., "Electric-field assisted assembly and alignment of metallic nanowires," *Applied Physics Letters*, vol. 77, no. 9, p. 1399, 2000.

- [20] W. U. Wang, C. Chen, K.-hui Lin, Y. Fang, and C. M. Lieber, "Label-free detection of small-molecule-protein interactions by using nanowire nanosensors.," *Proceedings of the National Academy of Sciences of the United States of America*, vol. 102, no. 9, pp. 3208-12, Mar. 2005.

- [21] Z. H. Chen, J. S. Jie, L. B. Luo, H. Wang, C. S. Lee, and S. T. Lee, "Applications of silicon nanowires functionalized with palladium nanoparticles in hydrogen sensors," *Nanotechnology*, vol. 18, no. 34, p. 345502, Aug. 2007.

- D1.1 Date of submission: 01/09/2011

- J. Kong, "Nanotube Molecular Wires as Chemical Sensors," Science, vol. 287, no. 5453, pp. [22] 622-625, Jan. 2000.

- E. C. Garnett, W. Liang, and P. Yang, "Growth and Electrical Characteristics of Platinum-[23] Nanoparticle-Catalyzed Silicon Nanowires," Advanced Materials, vol. 19, no. 19, pp. 2946-2950, Oct. 2007.

- K. Besteman, J.-O. Lee, F. G. M. Wiertz, H. A. Heering, and C. Dekker, "Enzyme-Coated [24] Carbon Nanotubes as Single-Molecule Biosensors," Nano Letters, vol. 3, no. 6, pp. 727-730, Jun. 2003.

- [25] J.-H. Ahn et al., "Heterogeneous three-dimensional electronics by use of printed semiconductor nanomaterials.," Science (New York, N.Y.), vol. 314, no. 5806, pp. 1754-7, Dec. 2006.

- M. S. Islam, S. Sharma, T. I. Kamins, and R. S. Williams, "Ultrahigh-density silicon nanobridges [26] formed between two vertical silicon surfaces," Nanotechnology, vol. 15, no. 5, p. L5-L8, May. 2004.

- T. I. Kamins, S. Sharma, A. A. Yasseri, Z. Li, and J. Straznicky, "Metal-catalysed, bridging [27] nanowires as vapour sensors and concept for their use in a sensor system," Nanotechnology, vol. 17, no. 11, p. S291-S297, Jun. 2006.

- C. Soci et al., "ZnO nanowire UV photodetectors with high internal gain.," Nano letters, vol. 7, [28] no. 4, pp. 1003-9, Apr. 2007.

- G. Rosaz et al., "High-performance silicon nanowire field-effect transistor with silicided [29] contacts," Semiconductor Science and Technology, vol. 26, no. 8, p. 085020, Aug. 2011.

- A. Potié et al., "Growth and characterization of gold catalyzed SiGe nanowires and alternative [30] metal-catalyzed Si nanowires.," Nanoscale research letters, vol. 6, no. 1, p. 187, Jan. 2011.

- M. Li et al., "Bottom-up assembly of large-area nanowire resonator arrays.," Nature [31] nanotechnology, vol. 3, no. 2, pp. 88-92, Feb. 2008.

- A. Javev, S. Nam, R. S. Friedman, H. Yan, and C. M. Lieber, "Layer-by-layer assembly of [32] nanowires for three-dimensional, multifunctional electronics.," Nano letters, vol. 7, no. 3, pp. 773-7, Mar. 2007.

- Z. Fan et al., "Wafer-scale assembly of highly ordered semiconductor nanowire arrays by [33] contact printing.," Nano letters, vol. 8, no. 1, pp. 20-5, Jan. 2008.

- R. Yerushalmi, Z. A. Jacobson, J. C. Ho, Z. Fan, and A. Javey, "Large scale, highly ordered [34] assembly of nanowire parallel arrays by differential roll printing," Applied Physics Letters, vol. 91, no. 20, p. 203104, Nov. 2007.

- Z. Fan, J. C. Ho, Z. A. Jacobson, H. Razavi, and A. Javey, "Large-scale, heterogeneous [35] integration of nanowire arrays for image sensor circuitry.," Proceedings of the National Academy of Sciences of the United States of America, vol. 105, no. 32, pp. 11066-70, Aug. 2008.

- S. Chen, J. G. Bomer, W. G. van der Wiel, E. T. Carlen, and A. van den Berg, "Top-down [36] fabrication of sub-30 nm monocrystalline silicon nanowires using conventional microfabrication.," ACS nano, vol. 3, no. 11, pp. 3485-92, Nov. 2009.

- Z. Gao et al., "Silicon nanowire arrays for label-free detection of DNA.," Analytical chemistry, [37] vol. 79, no. 9, pp. 3291-7, May. 2007.

- A. Kim et al., "Ultrasensitive, label-free, and real-time immunodetection using silicon field-effect [38] transistors," Applied Physics Letters, vol. 91, no. 10, p. 103901, Sep. 2007.

- E. Stern et al., "Label-free immunodetection with CMOS-compatible semiconducting [39] nanowires.," Nature, vol. 445, no. 7127, pp. 519-22, Feb. 2007.

- [40] Y. Chen, X. Wang, S. Erramilli, P. Mohanty, and A. Kalinowski, "Silicon-based nanoelectronic field-effect pH sensor with local gate control," Applied Physics Letters, vol. 89, no. 22, p. 223512, Nov. 2006.

- Z. Li, Y. Chen, X. Li, T. I. Kamins, K. Nauka, and R. S. Williams, "Sequence-Specific Label-[41] Free DNA Sensors Based on Silicon Nanowires," Nano Letters, vol. 4, no. 2, pp. 245-247, Feb.

- N. Elfström, R. Juhasz, I. Sychugov, T. Engfeldt, A. E. Karlström, and J. Linnros, "Surface [42] charge sensitivity of silicon nanowires: size dependence.," Nano letters, vol. 7, no. 9, pp. 2608-12, Sep. 2007.

- NANOFUNCTION D1.1 Date of submission: 01/09/2011

- [43] I. Park, Z. Li, A. P. Pisano, and R. S. Williams, "Selective surface functionalization of silicon nanowires via nanoscale joule heating.," *Nano Letters*, vol. 7, no. 10, pp. 3106-3111, 2007.

- [44] G.-J. Zhang et al., "DNA sensing by silicon nanowire: charge layer distance dependence.," *Nano letters*, vol. 8, no. 4, pp. 1066-70, Apr. 2008.

- [45] J. Wan et al., "Silicon nanowire sensor for gas detection fabricated by nanoimprint on SU8/SiO2/PMMA trilayer," *Microelectronic Engineering*, vol. 86, no. 4-6, pp. 1238-1242, Apr. 2009.

- [46] Z. Li, B. Rajendran, T. I. Kamins, X. Li, Y. Chen, and R. S. Williams, "Silicon nanowires for sequence-specific DNA sensing: device fabrication and simulation," *Applied Physics A*, vol. 80, no. 6, pp. 1257-1263, Mar. 2005.

- [47] A. I. Hochbaum et al., "Enhanced thermoelectric performance of rough silicon nanowires.," *Nature*, vol. 451, no. 7175, pp. 163-7, Jan. 2008.

- [48] N. Elfström and J. Linnros, "Avalanche breakdown in surface modified silicon nanowires," *Applied Physics Letters*, vol. 91, no. 10, p. 103502, Sep. 2007.

- [49] K. Peng, X. Wang, and S.-T. Lee, "Silicon nanowire array photoelectrochemical solar cells," *Applied Physics Letters*, vol. 92, no. 16, p. 163103, Apr. 2008.

- [50] R. Juhasz, N. Elfström, and J. Linnros, "Controlled fabrication of silicon nanowires by electron beam lithography and electrochemical size reduction.," *Nano letters*, vol. 5, no. 2, pp. 275-80, Feb. 2005.

- [51] N. Elfström, A. E. Karlström, and J. Linnros, "Silicon nanoribbons for electrical detection of biomolecules.," *Nano letters*, vol. 8, no. 3, pp. 945-9, Mar. 2008.

- [52] A. Agarwal, K. Buddharaju, I. Lao, N. Singh, N. Balasubramanian, and D. Kwong, "Silicon nanowire sensor array using top–down CMOS technology," *Sensors and Actuators A: Physical*, vol. 145-146, pp. 207-213, Jul. 2008.

- [53] I. Park, Z. Li, X. Li, A. P. Pisano, and R. S. Williams, "Towards the silicon nanowire-based sensor for intracellular biochemical detection.," *Biosensors & bioelectronics*, vol. 22, no. 9-10, pp. 2065-70, Apr. 2007.

- [54] A. Zhang, S. You, C. Soci, Y. Liu, D. Wang, and Y.-H. Lo, "Silicon nanowire detectors showing phototransistive gain," *Applied Physics Letters*, vol. 93, no. 12, p. 121110, Sep. 2008.

- [55] J. H. Chua, R.-E. Chee, A. Agarwal, S. M. Wong, and G.-J. Zhang, "Label-free electrical detection of cardiac biomarker with complementary metal-oxide semiconductor-compatible silicon nanowire sensor arrays.," *Analytical chemistry*, vol. 81, no. 15, pp. 6266-71, Aug. 2009.

- [56] E. Stern, R. Wagner, F. J. Sigworth, R. Breaker, T. M. Fahmy, and M. A. Reed, "Importance of the Debye screening length on nanowire field effect transistor sensors.," *Nano letters*, vol. 7, no. 11, pp. 3405-9, Nov. 2007.

- [57] C. Yang-Kyu, K. Tsu-Jae, and H. Chenming, "A spacer patterning technology for nanoscale CMOS," *IEEE Transactions on Electron Devices*, vol. 49, no. 3, pp. 436-441, Mar. 2002.

- [58] J. Hållstedt et al., "A robust spacer gate process for deca-nanometer high-frequency MOSFETs," *Microelectronic Engineering*, vol. 83, no. 3, pp. 434-439, Mar. 2006.

- [59] J. Bolten et al., "Improved CD control and line edge roughness in E-beam lithography through combining proximity effect correction with gray scale techniques," *Microelectronic Engineering*, vol. 87, no. 5-8, pp. 1041-1043, May. 2010.