# Large Scale Collaborative Project

# **DOTFIVE**

Towards 0.5 TeraHertz Silicon / Germanium Heterojunction bipolar technology

FP7 Contract Number: 216110

## WP2 - Evolutionary technology concepts

## **Deliverable report**

Due date of deliverable: M42 Actual submission date: M42

Deliverable ID: D2.4.2

Deliverable Title:

Results of ST SiGe HBT technology optimization

towards 500GHz f<sub>MAX</sub>

Responsible beneficiary: ST Contributing beneficiaries: ST

Start Date of the Project: 1 February 2008 42 Months

Revision: V1

Dissemination Level: PU

## PROPRIETARY RIGHTS STATEMENT

This document contains information, which is proprietary to the DOTFIVE Consortium. Neither this document nor the information contained herein shall be used, duplicated or communicated by any means to any third party, in whole or in parts, except with prior written consent of the DOTFIVE consortium.

### **Document Information**

**Document Name:** DOTFIVE-WP2-D2.4.2-<Confidential >

**Document ID:** DOTFIVE-WP2-D2. .2

Version: V1

**Version Date:** 28/07/11

Authors: P. Chevalier, A. Chantre

Security: Confidential

## **Approvals**

|                            | Name             | Organization | Date      | Visa |

|----------------------------|------------------|--------------|-----------|------|

|                            |                  |              |           |      |

| Coordinator                | Gilles THOMAS    | ST           | 23.8.2011 | Ok   |

| Technical Manager          | Michael Schröter | TUD          | 7.8.2011  | Ok   |

| Work Package<br>Leader WP2 | Thomas Meister   | IFX          | 7.8.2011  | Ok   |

| Quality Manager            | Patricia Kudelka | ALMA         | 23.8.2011 | Ok   |

## **Document history**

| Revision | Date     | Modification    | Authors                 |

|----------|----------|-----------------|-------------------------|

| V1       | 28/07/11 | Initial release | P. Chevalier A. Chantre |

|          |          |                 |                         |

|          |          |                 |                         |

|          |          |                 |                         |

|          |          |                 |                         |

|          |          |                 |                         |

|          |          |                 |                         |

Version: V1 - Date: 28/07/11

### Content

| Section | 1 - Executive summary                                                | 4  |

|---------|----------------------------------------------------------------------|----|

| 1.1     | Description of the deliverable content and purpose                   | 4  |

| 1.2     | Brief description of the state of the art and the innovation brought | 4  |

| 1.3     | Deviation from objectives                                            | 6  |

| 1.4     | If relevant: corrective actions                                      | 6  |

| 1.5     | Technological progress                                               | 6  |

| 1.6     | Analysis of the results                                              |    |

| 1.7     | Impact of the results                                                |    |

| 1.8     | IPR                                                                  |    |

| 1.9     | Publishable information                                              |    |

| 1.10    | Conclusion                                                           | 9  |

| Section | 2 - ANNEX                                                            | 11 |

| 2.1     | References                                                           | 11 |

Version: V1 - Date: 28/07/11 Security: PU

### **Section 1 - Executive summary**

#### 1.1 Description of the deliverable content and purpose

The objective of this deliverable is to provide the final status on the work done at STMicroelectronics within WP2. Process developments carried out on DPSA-SEG SiGe HBT architecture and related electrical results are detailed. First, results from last development phase - i.e. related to B4T technology - are updated, especially because electrical targets have been modified based on WP5 circuits results. Second, process trials targeting B5T technology are presented and analysed. It is shown that the final objective of 500 GHz  $f_{MAX}$  will not be met. A comparison with results obtained for other technologies studied in WP2 and WP3 shows the limitations of the DPSA-SEG architecture. Based on the developments done in WP3, proposals are made to overcome these limitations.

#### 1.2 Brief description of the state of the art and the innovation brought

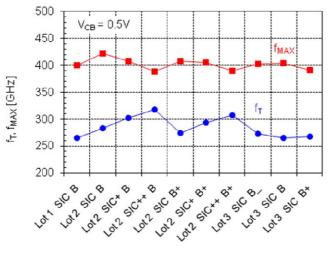

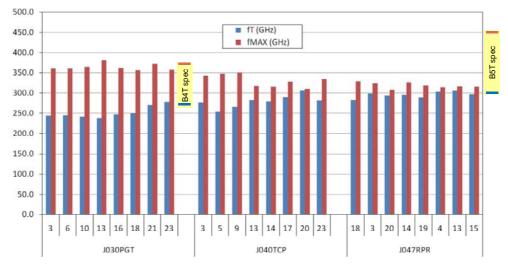

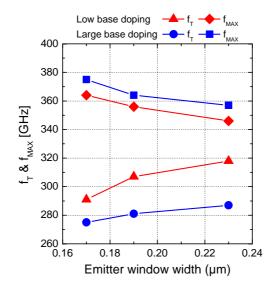

Results presented in [1] and summarized in Figure 1 show that  $f_T$  and  $f_{MAX}$  values of 300 GHz and 400 GHz respectively could be obtained simultaneously. They also confirm the well known trade-off between  $f_T$  and  $f_{MAX}$  related to the collector and base doping levels. One could be rather optimistic based on these results, since they were obtained with 110-nm wide emitters. Indeed, based on studies published in [2],  $f_{MAX}$  increase could be expected by further reduction of the emitter width. However, work described in [2] also pointed to the main risk associated with narrow emitters, which is the decrease of the transit frequency  $f_T$  due to the increase of the emitter resistance  $R_E$ . Therefore, developments were focused on two main aspects:

- 1. Evaluating a further lateral shrink based on B4T vertical profile

- 2. Investigating a shrink of the vertical profile in order to anticipate a degradation of  $f_{\mathsf{T}}$  due to the lateral shrink

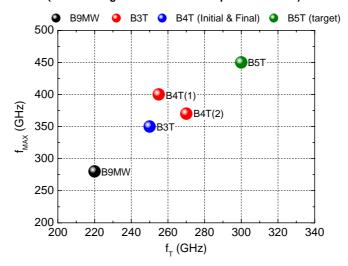

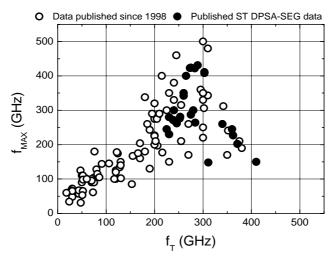

It is also worth pointing out that initial electrical targets of B4T technology have been revised, since better circuits results have been demonstrated in [3] with process changes leading to a larger f<sub>T</sub> (and lower f<sub>MAX</sub>). Therefore, B4T specifications have been modified from 250 GHz f<sub>T</sub> / 400 GHz f<sub>MAX</sub> to 270 GHz f<sub>T</sub> / 370 GHz f<sub>MAX</sub>. Although the modification at technology level was limited (increase of collector doping), this represented an important step since it brought back into question the objective of the project to focus on increasing f<sub>MAX</sub> while circuit results indicate the advantage of a more balanced device design. The evolution of HF performances between BiCMOS9MW and B5T (target) is plotted in Figure 2. Final B5T results are not yet available since the lot gathering all the developments presented in Section 1.5 is not yet completed its fabrication. However, it is very likely that the B5T objective will not be met with respect to  $f_{MAX}$ . Reaching  $f_T = 300$  GHz looks feasible, even if the reduction of the emitter width anticipated to increase  $f_{MAX}$  penalizes the emitter resistance. However, 450 GHz  $f_{MAX}$ seems out of reach since the reduction of the process thermal budget, applied to increase f<sub>T</sub>, degrades the extrinsic base resistance. Therefore, ~ 400 GHz f<sub>MAX</sub> appears to be the upper limit for this technology for  $f_T \ge 300$  GHz... Although this is ~100 GHz lower in  $f_{MAX}$  (cf. Figure 6) compared to the best obtained results [4], results obtained by ST in the project are still at the state-of-the-art for the DPSA-SEG architecture [5].

Version: V1 - Date: 28/07/11

Figure 1: f<sub>T</sub>, f<sub>MAX</sub> performances measured on 10 splits from 3 different lots using 400GHz f<sub>MAX</sub> SiGe HBT technology (wafer average values for 0.11×4.9µm² transistors)

Figure 2: f<sub>T</sub>, f<sub>MAX</sub> performances evolution between BiCMOS9MW and B5T (target) – 1: B9MW to B3T: Vertical & lateral scaling – 2: B3T to B4T(1): Lateral scaling only – 3: B4T(1) to B4T(2): Vertical scaling (increased collector doping) – 4: B4T(2) to B5T: Vertical & lateral scaling.

Figure 3: f<sub>MAX</sub> vs f<sub>T</sub> plot highlighting ST results obtained with DPSA-SEG architecture among all published data since 1998 (including recent DOTFIVE results to be published at BCTM'11).

Version: V1 - Date: 28/07/11

There is no deviation with respect to the work done in the project. However ST will not achieve 500 GHz  $f_{MAX}$  with its DPSA-SEG architecture. Explanations concerning the limitations of this architecture are given in Section 1.7. However, data on ring oscillator gate delay are expected for the final review, and the 2.5 ps objective may still be met.

#### 1.4 If relevant: corrective actions

No corrective action is planned today, since not being able to meet the 500 GHz  $f_{MAX}$  objective with DPSA-SEG architecture is not considered as a deviation from objectives, but rather as one of the conclusions of the project.

### 1.5 Technological progress

As mentioned in Section 1.2, technological progress focused on one hand on the evaluation of a further lateral shrink based on B4T vertical profile, and on the other hand on the shrink of the vertical profile in order to anticipate a degradation of  $f_T$  due to the lateral shrink. 3 lots of 25 wafers, combining trials on both vertical and lateral scaling, have been used for these studies (J030PGT, J040TCP and J047RPR).

Experiments on the downscaling of the vertical profile were based on the studies published in [6] and therefore could be considered as 'conventional'. They included variations on buried layer doping and collector doping (SIC), reduction of the spike annealing temperature from 1080°C to 1050°C, and adaptation of the base profile to the modified thermal budget. Variations on base doping concentration have been performed too. Furthermore, ion implantations determining values of resistances offered in the Design Kit have been modified in order to account for changes in activation annealing temperature.

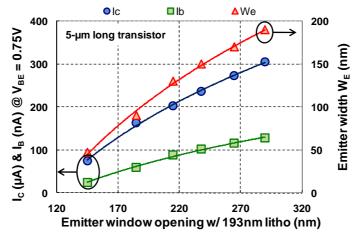

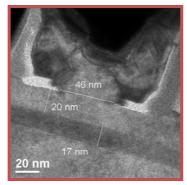

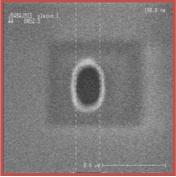

Most of the efforts were devoted to the lateral shrink, with the development of 193-nm lithography both for emitter window and polyemitter patterning. This led to significant process changes, since the SIC module had to be moved before the emitter window patterning in order to cope with the reduced resist thickness. This change had a major impact on base cavity opening [7]. The inside spacer module has also been modified, in order to reduce the spacer width from ~75nm to ~40nm, and the associated extrinsic base resistance component. Figure 4 shows the evolution of collector current (I<sub>C</sub>), base current (I<sub>B</sub>), and effective emitter width (W<sub>E</sub>) with emitter window opening, using 193-nm lithography. It demonstrates that W<sub>E</sub> as narrow as 45nm, illustrated in Figure 5 (left), can be achieved without using any Optical Proximity Correction. Moreover, Figure 5 (right) shows that emitter window lengths as small as 0.4  $\mu$ m can be defined for an emitter window width of 0.19  $\mu$ m, again without any OPC.

Figure 4: Evolution of the collector (I<sub>C</sub>) and base (I<sub>B</sub>) currents, and of the effective emitter window opening obtained by using 193-nm lithography & modified inside spacers' module.

Version: V1 - Date: 28/07/11

Figure 5: Cross-section of a transistor with an effective emitter width (W<sub>E</sub>) of 45nm (left) and top view of 190-nm wide and 400-nm long emitter window opening (right), both obtained by using 193-nm lithography.

#### 1.6 Analysis of the results

Results obtained on vertical scaling experiments performed on the 3 lots aforementioned are summarized in Figure 6. They show that while the  $f_T$  increase was successful, not surprisingly, it was accompanied by a decrease of  $f_{MAX}$ . As explained in Section 1.2, it is the objective of the lateral scaling to increase  $f_{MAX}$  by reducing both the base resistance (intrinsic part related to  $W_E$ ) and the collector/base capacitance (related to the collector/base junction area). Figure 7 presents the evolution of  $f_T$  and  $f_{MAX}$  with the emitter window width for 2 vertical profiles, which are potential candidates for the B5T technology. It confirms that  $f_T$  is negatively impacted by the increase of the emitter resistance. This penalizes the increase of  $f_{MAX}$  brought by the reduction of the intrinsic base resistance, which is degraded by the reduction of the thermal budget too.

The process and layout modifications selected for the B5T technology (last ST run), compared to the B4T technology, can be summarized as follows:

- Increase of the collector doping (buried layer)

- Reduction of the spike annealing temperature from 1080°C to 1050°C

- Modification of the base profile accordingly, and increase of the base doping to minimize the degradation of the base resistance

- Reduction of the emitter window width from 230 nm to 180 nm, but modification of the inside spacer module to get the same final effective emitter width (100 nm).

Electrical results from the actual B5T technology are expected end of August 2011.  $f_{MAX}$  is not expected to exceed 400 GHz ( $f_{T}$  ~300 GHz).

Figure 6: f<sub>T</sub>, f<sub>MAX</sub> performances measured on 24 splits done on vertical profile from 3 different lots with B4T design rules (wafer average values for 0.11×4.9µm² transistors)

Version: V1 - Date: 28/07/11

Figure 7: f<sub>T</sub>, f<sub>MAX</sub> evolution with the emitter window width for 2 different process splits on base doping performed on lot J040TCP.

#### 1.7 Impact of the results

The main purpose of these results is to outline the limitations of the DPSA-SEG architecture. as developed by ST. A detailed comparison of the results obtained on the various architectures investigated in WP2 and WP3 has been done in the frame of an invited paper at the 2011 Bipolar/BiCMOS Technology Meeting [5]. The first generation of ST B4T technology, i.e. with reduced collector doping, is compared to other DOTFIVE partners' architectures in Table 1. B4T technology exhibits the largest base resistance (cf. (R<sub>B</sub>+R<sub>F</sub>)×L<sub>F</sub>). A better result is obtained on IFX DPSA-SEG HBT, which could be explained by the possibility offered in this technology to optimize the base link resistance independently from the final anneal (not possible in ST technology due to the constraint of CMOS compatibility). These electrical parameters (obtained by a model parameter extraction) are not yet available for ST B5T technology, but it is expected that the base resistance will be even larger due to the increased weight of the extrinsic component R<sub>Bx</sub>. Therefore, any reduction of the intrinsic base resistance component, brought by the emitter width reduction, is counterbalanced by an increase of R<sub>Bx</sub>. A reduction of R<sub>Bx</sub> with the current architecture may be possible by modyfying the ion implantation conditions of the polybase, or by replacing it by a boron in-situ doped polybase. However, a strong reduction of R<sub>Bx</sub> to the value of the IHP2 HBT in Table 1 will likely require a similar technological solution as the ones developed for the IHP2 and IMEC HBTs, i.e. the deposition of the external base after the growth of the intrinsic base.

This is a very important conclusion since developments done at ST on DPSA-SEG SiGe HBT architecture are being used for the start of a new BiCMOS technology based on 55nm CMOS. Indeed, the final spike annealing temperature in 55nm CMOS is 1050°C and therefore the same  $f_{MAX}$  limitation due to  $R_{Bx}$  is anticipated. Evaluations have started to determine whether major architecture modifications have to be adopted in 55 nm SiGe BiCMOS, based on the electrical specifications currently being discussed with ST customers.

Version: V1 - Date: 28/07/11

Table 1 Comparison of the main electrical characteristic of the different HBTs developed in DotFive (from [5])

| Parameter                                          | Unit         | IFX        | ST          | IHP1       | IMEC       | IHP2      |

|----------------------------------------------------|--------------|------------|-------------|------------|------------|-----------|

| $W_{E}$                                            | μm           | 0.13       | 0.10        | 0.16       | 0.08       | 0.12      |

| L <sub>E</sub>                                     | μm           | 2.70       | 4.90        | 0.93       | 0.93       | 0.96      |

| n <sub>E</sub>                                     | -            | 1          | 1           | 2          | 1          | 8         |

| Contacts #                                         | -            | 1E/1B/1C   | 1E/2B/2C    | 2E/2B/2C   | 1E/2B/1C   | 8E/8B/8C  |

| A <sub>E</sub>                                     | μm²          | 0.351      | 0.490       | 0.298      | 0.074      | 0.922     |

| Peak f <sub>T</sub>                                | GHz          | 240        | 260         | 300        | 215        | 300       |

| $J_{C,peak}$                                       | mA/μm²       | 10.0       | 14.3        | 16.0       | 17.5       | 18.5      |

| f <sub>MAX</sub>                                   | GHz          | 380        | 400         | 350        | 400        | 500       |

| β (V <sub>BE</sub> , V)                            | -            | 1300 (0.6) | 2100 (0.65) | 250 (0.87) | 800 (0.75) | 700 (0.7) |

| BV <sub>EBO</sub>                                  | ٧            | 2.3        | 1.7         | 1.5        | 2.1        | 1.7       |

| BV <sub>CBO</sub>                                  | V            | 5.5        | 6.0         | 4.3        | 5.2        | 5.2       |

| BV <sub>CEO</sub>                                  | V            | 1.50       | 1.55        | 1.85       | 1.70       | 1.60      |

| V <sub>A</sub>                                     | V            | 110        | 270         | 85         | 60         | 180       |

| Rs <sub>pbi</sub>                                  | $k\Omega/sq$ | 2.6        | 2.5         | 3.3        | 2.7        | 2.6       |

| C <sub>BE</sub>                                    | fF           | 5.2        | 9.7         | 4.4        | 2.7        | 20.1      |

| C <sub>BC</sub>                                    | fF           | 3.5        | 6.1         | 3.4        | 1.6        | 13.9      |

| C <sub>CS</sub>                                    | fF           | 2.4        | 4.1         | 4.0        | 4.3        | 8.5       |

| R <sub>E</sub>                                     | Ω            | 3.8        | 2.3         | 6.5        | 40.0       | 2.3       |

| R <sub>B</sub>                                     | Ω            | 28.2       | 24.0        | 51.1       | 35.0       | 4.7       |

| R <sub>CX</sub>                                    | Ω            | 9.2        | 4.0         | 10.5       | -          | 4.8       |

| $\tau_{D}$                                         | ps           | 2.4        | -           | 2.5        | -          | 2.0       |

| R <sub>E</sub> x A <sub>E</sub>                    | Ω.μm²        | 1.33       | 1.13        | 1.93       | 2.98       | 2.12      |

| (R <sub>B</sub> +R <sub>E</sub> ) x L <sub>E</sub> | Ω.μm         | 86         | 129         | 107        | 70         | 54        |

| R <sub>CX</sub> x A <sub>E</sub>                   | Ω.μm²        | 3.23       | 1.96        | 3.12       | -          | 5.21      |

| C <sub>BE</sub> / A <sub>E</sub>                   | fF/μm²       | 14.8       | 19.8        | 14.8       | 36.3       | 21.8      |

| C <sub>BC</sub> / A <sub>E</sub>                   | fF/μm²       | 10.0       | 12.4        | 11.4       | 20.8       | 15.1      |

| C <sub>CS</sub> / A <sub>E</sub>                   | fF/μm²       | 6.8        | 8.4         | 13.4       | 57.8       | 9.2       |

I am not aware of any time constant that contains Rcx\*AE. In my opinion, a better figure would be Rcx\*LE (all devices considered have sufficiently long fingers), assuming the distance between C and E contact edge to be similar for all processes.

#### 1.8 IPR

NA.

### 1.9 Publishable information

An invited paper is going to be published at the 2011 Bipolar/BiCMOS Circuits and Technology Meeting [5]. This paper, written in cooperation with all partners involved in WP2 and WP3 (ST, IFX, IHP and IMEC), presents the status of the technogical developments done within the Project.

#### 1.10 Conclusion

State-of-the-art results have been demonstrated for the DPSA-SEG SiGe HBT architecture, whose main advantage is to offer an overall simple fabrication process. Furthermore, manufacturability of this solution has been demonstrated since the 2 partners involved in

Version: V1 - Date: 28/07/11

WP2 use this architecture for technologies already in production (B7HF200 at IFX and BiCMOS9MW at ST). The limitations of this architecture have been clearly identified however, and 400 GHz f<sub>MAX</sub> was hardly exceeded (430GHz f<sub>MAX</sub> is the largest value which has been measured [1]), especially when large f<sub>T</sub> values are targeted too. Trials are still ongoing but 300 GHz f<sub>T</sub> / 400 GHz f<sub>MAX</sub> is probably today the best performance trade-off expected from this technology without major process modifications. On the other hand, such performance may be sufficient for next generation BiCMOS which has started at ST on 55 nm CMOS node. 55 nm SiGe BiCMOS will largely benefit from the developments done in DOTFIVE. It is also possible that a larger f<sub>MAX</sub> will be targeted in 55 nm BiCMOS. If this is the case, developments done in WP3 give some clues since the main limitations of the DPSA-SEG architectures have been successfully adressed in this workpackage. Indeed, as could be expected, the best results in DOTFIVE have been obtained with the new architectures developed in WP3 [4][8]. Of course, some innovations are available at the expense of process complexity but developments done by IHP in WP3 open up the road for the modifications to be done to overcome the limitations of the conventional DPSA-SEG architecture [9][10].

Version: V1 - Date: 28/07/11

### Section 2 - Annex

#### 2.1 References

[1] A. Chantre, P. Chevalier, T. Lacave, G. Avenier, M. Buczko, Y. Campidelli, L. Depoyan, L. Berthier, C. Gaquière, "Pushing Conventional SiGe HBT Technology Towards 'Dotfive' Terahertz", in Proc. 5<sup>th</sup> European Microwave Integrated Circuits Conference, 2010, pp. 21–24

[2] P. Chevalier, F. Pourchon, T. Lacave, G. Avenier, Y. Campidelli, L. Depoyan, G. Troillard, M. Buczko, D. Gloria, D. Céli, C. Gaquière, A. Chantre, "A Conventional Double-Polysilicon FSA-SEG Si/SiGe:C HBT Reaching 400 GHz f<sub>MAX</sub>", BCTM Proc., 2009, pp. 1-4.

[3] E. Öjefors, F. Pourchon, P. Chevalier, and U. R. Pfeiffer, "A 160-GHz low-noise downconverter in a SiGe HBT technology," in European Microwave Conf. (EuMC), Oct. 2010, pp. 521–524

[4] B. Heinemann, R. Barth, D. Bolze, J. Drews, G. G. Fischer, A. Fox, O. Fursenko, T. Grabolla, U. Haak, D. Knoll, R. Kurps, M. Lisker, S. Marschmeyer, H. Rücker, D. Schmidt, J. Schmidt, M. A. Schubert, B. Tillack, C. Wipf, D. Wolansky, Y. Yamamoto, "SiGe HBT Technology with  $f_T/f_{max}$  of 300GHz/500GHz and 2.0 ps CML Gate Delay", IEDM Digest, 2010, pp. 688-691

[5] P. Chevalier, T.F. Meister, B. Heinemann, S. Van Huylenbroeck, W. Liebl, A. Fox, A. Sibaja-Hernandez and A. Chantre, "Towards THz SiGe HBTs", Proc. of the Bipolar/BiCMOS Technology Meeting, 2011, in press

[6] T. Lacave, P. Chevalier, Y. Campidelli, M. Buczko, L. Depoyan, L. Berthier, G. Avenier, C. Gaquière, A. Chantre, "Vertical Profile Optimization for +400 GHz f<sub>MAX</sub> Si/SiGe:C HBTs", BCTM Proc., 2010, pp. 49-52

[7] T. Lacave et al, "Influence of the Selectively Implanted Collector Integration on +400 GHz f<sub>MAX</sub> Si/SiGe:C HBTs", SiGe workwhop of the 218<sup>th</sup> ECS meeting

[8] S. Van Huylenbroeck, A. Sibaja-Hernandez, R. Venegas, S. You, F. Vleugels, D. Radisic, W. Lee, W. Vanherle, K. De Meyer, S. Decoutere, "Pedestal Collector Optimization for High Speed SiGe:C HBT", BCTM Proc., 2011, in press.

[9] A. Fox, B. Heinemann, R. Barth, D. Bolze, J. Drews, U. Haak, D. Knoll, B. Kuck, R. Kurps, S. Marschmeyer, H.H. Richter, H. Rücker, P. Schley, D. Schmidt, B. Tillack, G. Weidner, C. Wipf, D. Wolansky, Y. Yamamoto, "SiGe HBT Module with 2.5 ps Gate Delay", IEDM Digest, 2008, pp. 731-734.

[10] A. Fox, B. Heinemann, R. Barth, S. Marschmeyer, Ch. Wipf, Y. Yamamoto, "SiGe:C HBT Architecture with Epitaxial External Base", BCTM Proc., 2011, in press

Version: V1 - Date: 28/07/11